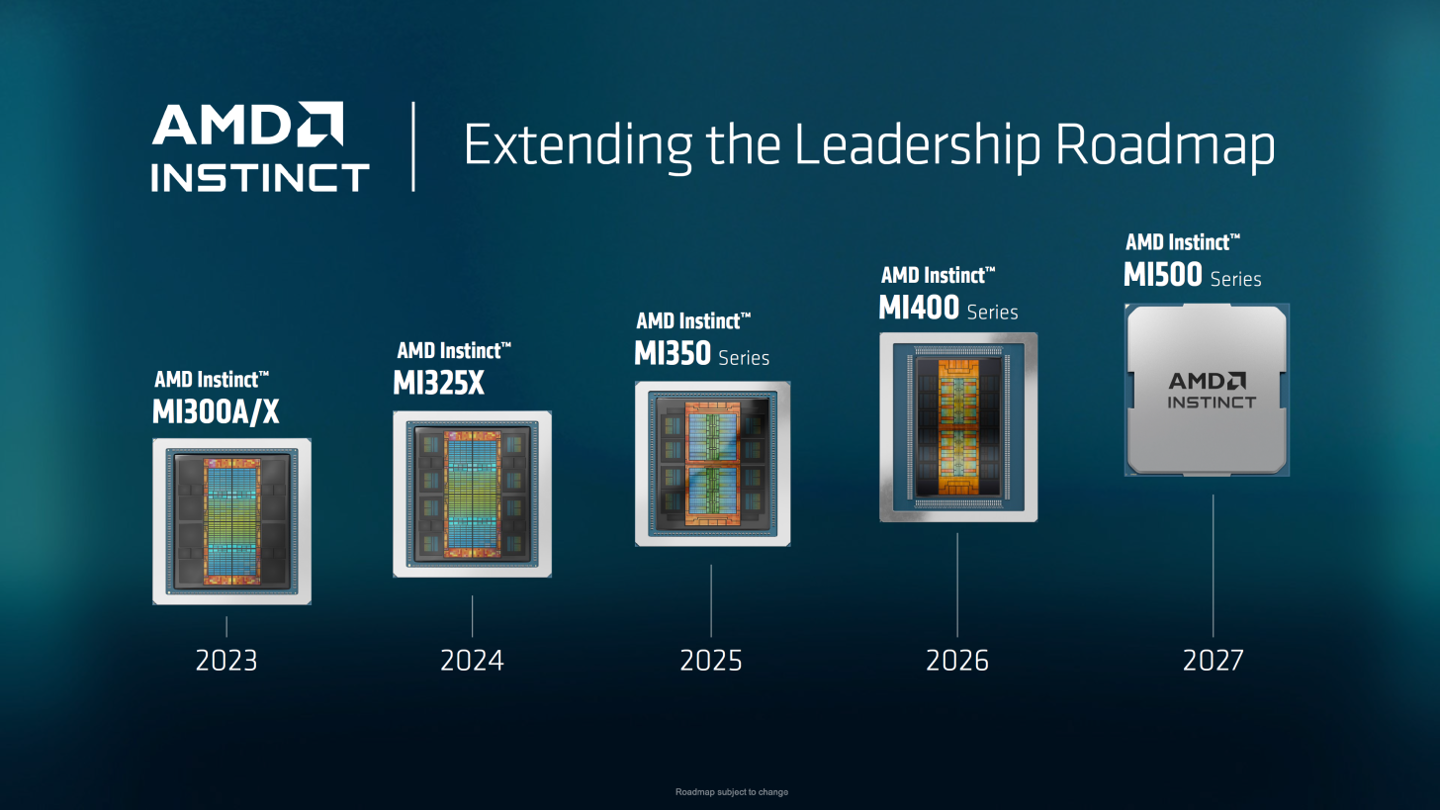

AMD AI 加速器 MI500 前瞻:CPO 封装、CDNA 6 架构、内存带宽将超 19.6 TB/s

3 小时前

/ 阅读约2分钟

来源:IT之家

AMD与格罗方德合作开发下一代Instinct MI500 AI加速器的MRM共封装光学解决方案,采用2nm工艺,搭载HBM4E内存,内存带宽将超越MI400。英伟达也在推进CPO技术。

IT之家 4 月 21 日消息,科技媒体 Wccftech 昨日(4 月 20 日)发布博文,报道称 AMD 为了在硅光技术领域应对英伟达的竞争,将与格罗方德(GlobalFoundries)合作开发下一代 Instinct MI500 AI 加速器的 MRM 共封装光学解决方案。

IT之家注:MRM 全称为 Micro-Ring Modulator,是一种关键的硅光子技术组件,用于高效转换电信号到光信号。该技术利用硅基材料制造微环结构,通过调制光波的相位或强度来传输数据。

共封装光学解决方案(Co-Packaged Optics,简称 CPO)通过减少对铜线的依赖,利用光信号传输数据,从而降低互连延迟并建立 CPU 与 GPU 间的高带宽连接。

基于最新披露的合作细节,格罗方德负责制造光子集成电路,日月光半导体(ASE)负责封装,而 AMD 去年收购的 Enosemi 公司,负责加速相关创新。

MI500 系列将基于比 MI400 更先进的 2nm 工艺打造,由台积电代工。该加速器将采用 CDNA 6 架构,搭载 HBM4E 内存,其内存带宽将超越 MI400 的 19.6 TB/s。

消息称英伟达同样在推进 CPO 技术,其 Vera Rubin 加速器将采用台积电制造的 PIC,由矽品精密工业(SPIL)负责封装。

对于 Rubin Ultra,英伟达将优先采用 CPO 方案,未来 Feynman 世代 AI 加速器计划全面转向 CPO 技术,彻底淘汰近封装光学技术(NPO)方案。