在算力时代,随着英伟达GPU与AI芯片浪潮的迅猛发展,CoWoS封装技术凭借其独特优势迅速崛起,一度成为行业焦点,市场需求旺盛到供不应求的地步。

然而,伴随技术应用的不断深入和行业发展的持续推进,芯片集成正朝着更大面积、更高集成度、更短互连长度的系统级创新方向演进。CoWoS封装技术逐渐显露出一系列不容忽视的缺点与挑战:其工艺的复杂性不仅推高了生产成本,还带来了良率控制与测试环节的诸多难题;同时,在互连性能、电源完整性等电气特性方面也面临着严峻考验,再加上台积电长期存在的产能瓶颈,这些问题交织在一起,已成为制约行业发展的不小困扰。

正因如此,当前业界正将目光投向新的封装技术领域,积极探寻能够有效替代CoWoS的解决方案。

CoWoS之后,封装技术的迭代与竞逐

CoPoS,化圆为方

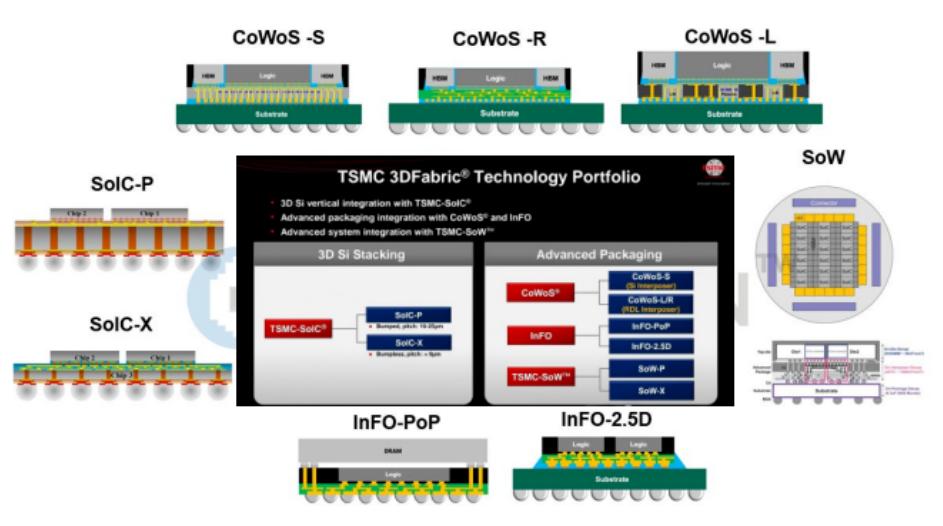

当前,CoWoS技术主要由台积电掌握。从短期技术演进路径来看,台积电正推动CoWoS从现有CoWoS-S/CoWoS-R版本向更具潜力的CoWoS-L技术升级——相比前代产品,CoWoS-L在灵活性与经济性等核心指标上均实现了显著优化。

然而,随着AI GPU芯片尺寸的增大以及HBM堆栈数量的增加,CoWoS遇到了瓶颈——光刻掩模尺寸限制了单一模块的最大封装面积。

为了应对这一挑战,业界普遍认为CoPoS技术将成为CoWoS的未来演进方向。对此台积电也明确表示将CoPoS定位为CoWoS的下一代继任者,并计划在未来通过技术迭代逐步完成对CoWoS-L的替代。

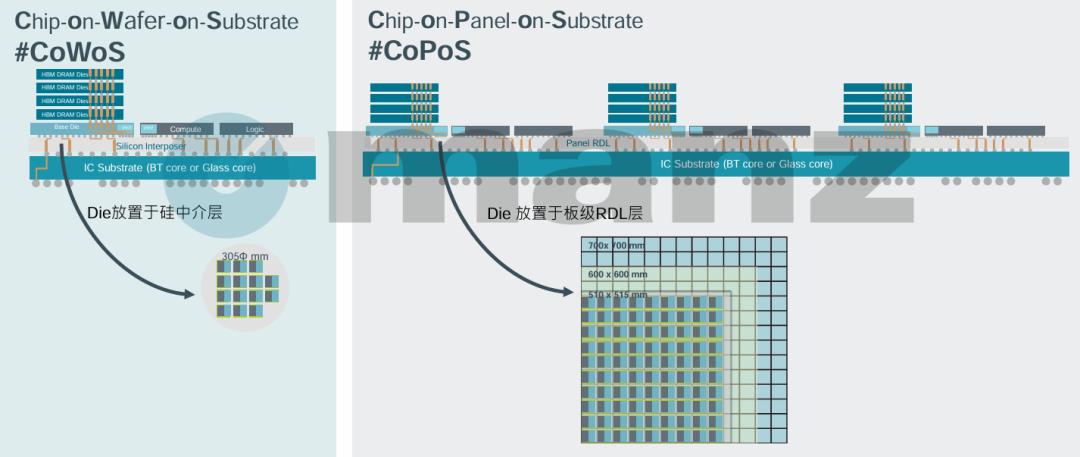

众所周知,CoWoS(Chip-on-Wafer-on-Substrate)属于晶圆级封装,其将芯片堆叠起来再封装于基板上,最终形成2.5D、3D的形态,能减少芯片空间,还可降低功耗和成本;而CoPoS (Chip-on-Panel-on-Substrate)可以看作是CoWoS的面板化解決方案。

从技术架构来看,CoPoS与CoWoS一脉相承,核心差异在于将CoWoS中的硅中介层替换为面板尺寸基板(即面板级重布线层)——这一关键升级使其得以突破现有技术瓶颈,实现更大的封装尺寸、更优的面积利用率和更大的生产灵活性与可扩展性。

图源:manz

CoPoS核心理念是将“圆形变为方形”——用大型矩形面板基板替换晶圆级封装,减少圆形晶圆边缘通常出现的不完整芯片。

这种设计变化促进了单一封装内更多半导体的集成,从而提高整体计算性能,实现了更高的基板利用率、更大的封装密度、改进的良率效率、减少的边缘浪费和更低的单位面积成本。例如,CoPoS采用600mm×600mm、700mm×700mm或310mm×310mm等面板级封装规格,提供了更多的封装空间、更高的I/O集成和改进的生产效率,使其成为CoWoS平台的自然演进。

实际上,CoPoS并非简单的将硅中介层换成panel(面板)来实现“由圆变方”,而是一场涉及材料、工艺、设备的全方位革新。

为支持这一结构转变,必须显著增强重布线层(RDL)工艺,以适应多层金属堆叠、高I/O密度和多芯片集成等广泛的封装要求。

同时,随着封装面积和功率密度的增加,台积电还引入了先进材料和技术——如玻璃基板和玻璃通孔(TGV)——这些材料提供了卓越的平整度、热稳定性和垂直互连能力,从而改善热性能和互连灵活性。

事实上,玻璃基板对于CoPoS工艺也非常重要。

因具备低热膨胀系数、高机械强度、耐高温性、高布线密度等特点,玻璃基板被视为半导体下一代基板解决方案。早在2023年9月份,英特尔便公开宣布其在玻璃核心基板方面的努力,认为该技术将重新定义芯片封装的边界,为数据中心、人工智能和图形处理提供具有突破性的解决方案,推动摩尔定律的进一步发展。在英特尔带头亮出玻璃基板技术后,业界对该议题兴趣颇深,正在推动产业链厂商加大对该技术的投入,有望在几年之内就能看到比较清晰的进程和突破。

从市场进展来看,CoWoS和CoPoS都是台积电主导的先进封装技术。目前,台积电已启动CoPoS试点线,据悉台积电将于2026年在其子公司采钰设立首条CoPoS封装技术实验线。与此同时,用于大规模生产的CoPoS量产工厂也已确定选址嘉义AP7,目标是在2028年底至2029年间实现该技术的大规模量产,首家客户将由英伟达拔得头筹。

展望未来,CoWoS和CoPoS均聚焦HBM与处理器的协同优化。随着AI对算力需求激增,CoWoS-R/L和CoPoS将并行发展——前者满足性能优先场景,后者推动规模化量产,共同支撑3D封装生态

行业巨头,涌向FOPLP赛道

最近,业内关于FOPLP先进封装的消息频传。

- 马斯克旗下的SpaceX公司意图涉足面板级扇出型封装(FOPLP),且计划在德州建设自家芯片封装厂,其基板尺寸达到700mm×700mm,为业界最大;

- 日月光投入2亿美元采购设备,在高雄厂建立产线,计划今年年底试产FOPLP;

- 英伟达去年就在计划提前为其 GB200 AI 服务器芯片采用FOPLP技术,旨在解决台积电CoWoS封装产能紧张的问题。

业内人士指出,在AI芯片封装领域,FOPLP有望成为CoWoS 的主要替代技术之一。

要理解面板级扇出型封装(FOPLP),需先追溯其技术源头——扇出型晶圆级封装(Fan-Out Wafer Level Packaging,FOWLP)。该技术由英飞凌于2004年提出,并在 2009 年实现量产,但早期仅应用于手机基带芯片,很快便面临市场饱和。直到 2016 年,台积电在 FOWLP 基础上开发出整合扇出型(Integrated Fan-Out,InFO)封装,成功应用于苹果 iPhone 7 系列的 A10 处理器,才重新推动半导体产业加速布局 FOWLP 技术。

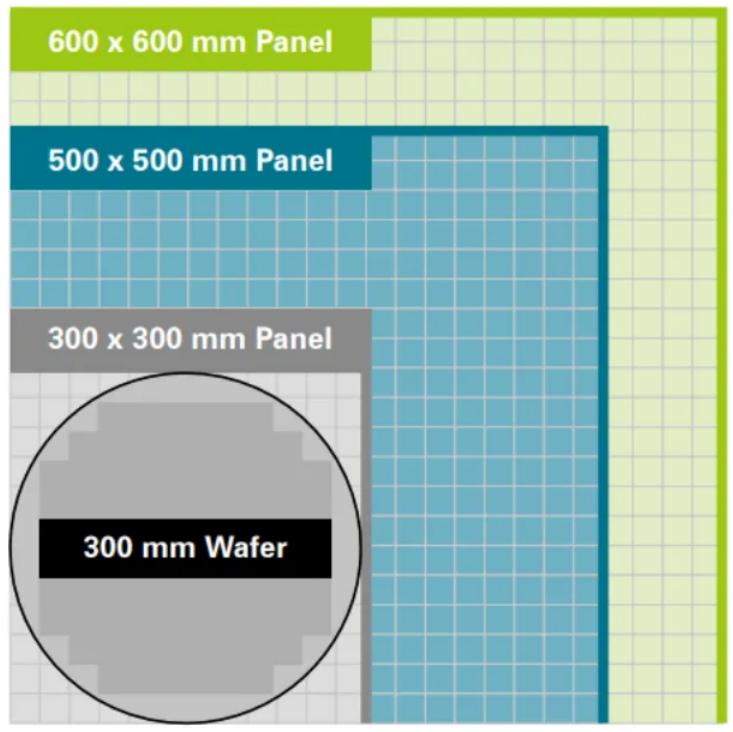

作为FOWLP的延伸技术,FOPLP继承了前者高I/O密度、薄型化设计的核心优势,两者的关键差异仅在于载体形式——从“晶圆(Wafer)”替代为“面板(Panel)”,而这一字之差直接带来了尺寸与利用率的显著提升。

具体而言,FOPLP是扇出式封装(Fan Out)与面板级封装(Panel Level Package)的技术融合,兼具两类技术的核心优点:

- 依托扇出式封装特性,其重布线层(RDL)走线可突破芯片尺寸限制,支持更多外部I/O接口,实现高密度连接与薄型化封装,在降低成本的同时满足产品轻薄化需求;

- 凭借面板级封装优势,采用金属、玻璃或高分子聚合物作为载板,可实现更大封装尺寸与更高生产灵活性。其面积利用率超95%,显著高于传统晶圆级封装的85%,并具备批量生产能力强、成本低、周期短等特点——与圆形晶圆相比,面板型封装的成本可节省20%以上。

随着人工智能技术的发展,大尺寸芯片封装需求日益凸显,FOPLP因此受到业界广泛关注。

作为扇出型封装的两大主流技术,FOWLP与FOPLP的发展路径截然不同:FOWLP聚焦晶圆直接封装,侧重实现更小体积与更高集成度,适用于CPU、GPU、FPGA等大型芯片;而FOPLP通过面板级封装满足更广泛场景需求,包括高功率、大电流功率半导体,且无需依赖最先进工艺与设备,技术实现门槛更低。

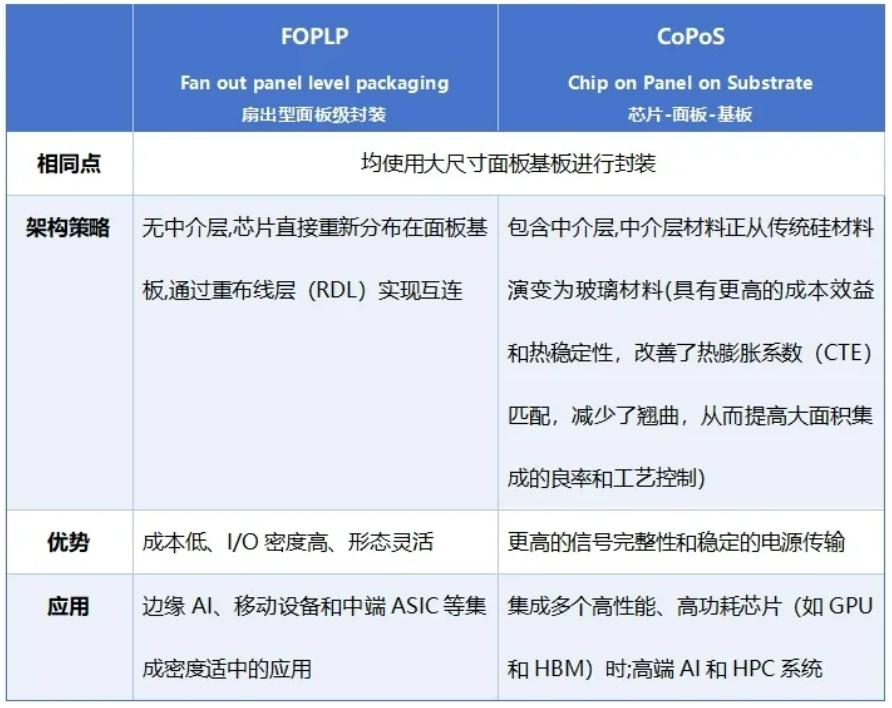

值得注意的是,FOPLP封装技术与面板工艺密切相关,但与上面提到的CoPoS在工艺策略与性能适用上存在差异:

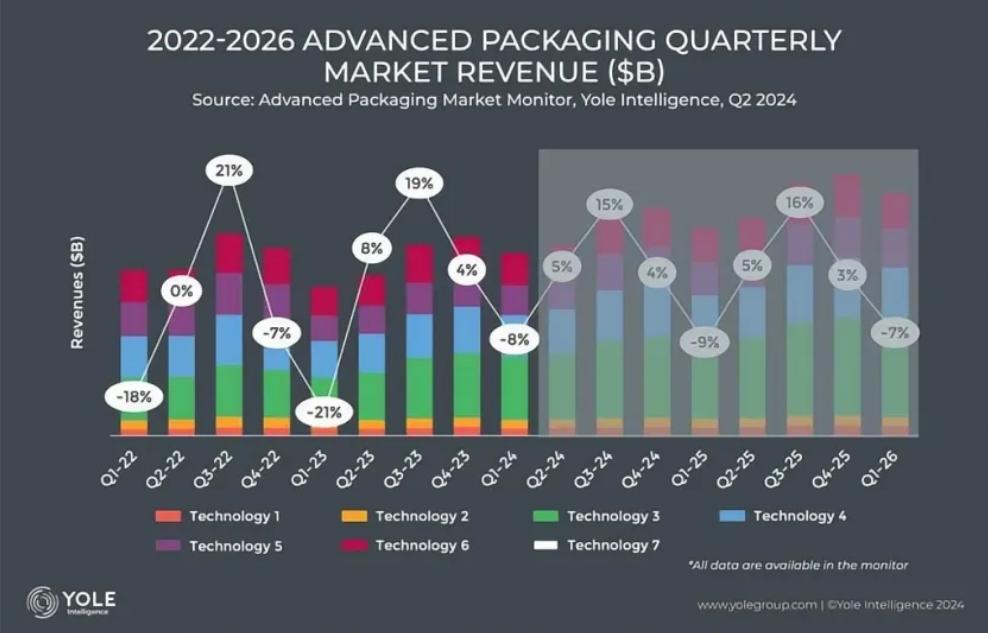

市场分析机构Yole统计数据显示,2022年FOPLP市场规模约为4100万美元,预计未来五年将呈现32.5%的复合年增长率,到2028年增长到2.21亿美元。未来,随着更多厂商的布局和推动,以及更高良率带来更好的成本效益,FOPLP有望在未来几年实现增长。

面对巨大市场潜力,业界当前已将面板级封装视为下一代先进封装技术的关键战场,吸引了各大巨头投身其中,积极发展FOPLP封装技术。

●行业巨头,涌向FOPLP赛道

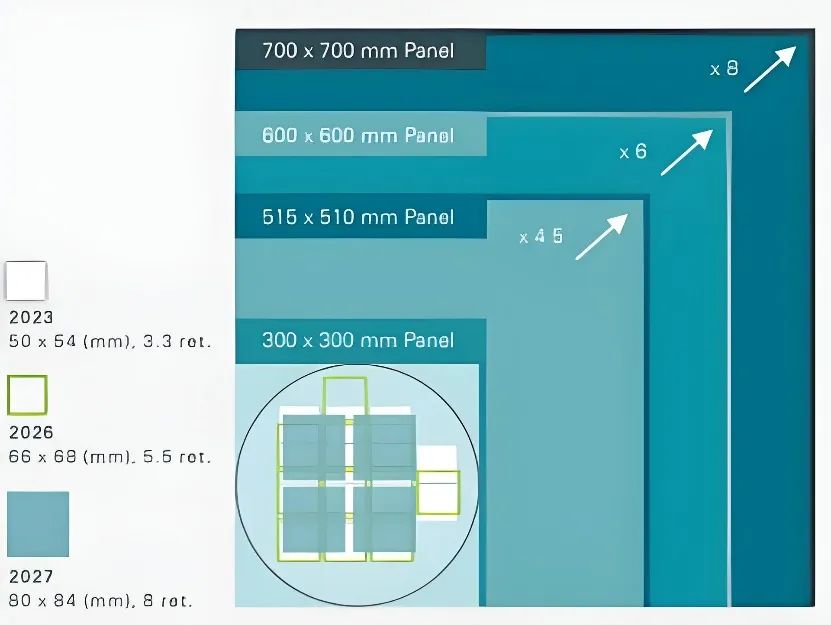

日月光在FOPLP领域布局已久,十年前便启动相关研发工作。其初期采用300mm×300mm规格进行技术验证,在试作效果达标后,将尺寸推进至600mm×600mm,并于去年完成设备采购下单。

今年2月,日月光投控营运长吴田玉宣布,将在中国台湾高雄厂区投入2亿美元建设FOPLP量产线,涵盖Chip First、RDL First及玻璃通孔(TGV)等关键工艺模块,目标是将现有 FOWLP 技术能力扩展至更大面积封装与异构集成领域,以满足 AI、高性能计算、汽车电子及存储模块等市场的增长需求。

按照规划,相关设备于第二季进厂,第三季启动试量产;600mm×600mm规格机台预计今年底完成试产,若进展顺利,明年送样客户验证通过后即可正式量产出货。若600mm×600mm封装良率能达到预期,则有望吸引更多客户与产品导入,推动该规格成为业界主流。

作为先进封装领域的重要参与者,三星同样对FOPLP工艺展现出浓厚兴趣。据报道,三星早在2019年便以7850亿韩元从三星电机手中收购面板级封装(PLP)业务,这一战略布局为其后续在该领域的发展奠定了基础。

在去年3月的股东大会上,时任三星电子半导体部门负责人Kyung Kye-hyun曾指出,AI半导体芯片通常需要600mm×600mm甚至800mm×800mm的大尺寸封装,这类需求正需要PLP等技术支撑,而三星当时已在积极推进相关技术研发并展开客户合作。目前,三星已开始部署面向先进制程的FOPLP技术,其应用于可穿戴设备的Exynos W920 处理器便采用了5nm EUV工艺与FOPLP封装方案,实现了技术落地。

台积电同样是FOPLP技术的积极推动者。目前其正紧锣密鼓地推进FOPLP工艺研发,不仅已组建专门的研发团队,还规划了专属生产线,不过整体仍处于起步阶段。2024年8月,台积电发布公告称计划斥资171.4亿元新台币向群创购买南科厂房及附属设施;据去年年底的消息显示,台积电初期将选择尺寸较小的300×300mm面板切入FOPLP领域,预计最快2026年完成小规模试产线的建设。

报道指出,台积电最初曾倾向采用515×510mm 矩形基板——与传统12英寸圆形晶圆相比,该规格基板的可用面积可提升三倍。此后其又陆续测试了600×600mm、300×300mm等不同尺寸,最终决定初期以300×300mm规格“练兵”,待技术成熟后再向更大尺寸拓展。这一决策主要基于两方面考量:一是设备持有成本的控制,二是现有技术可支持的最大光罩尺寸限制。

值得注意的是,当前FOPLP技术仍处于开发阶段,配套设备与工艺尚未完全成熟,在大尺寸基板边缘翘曲、运输过程损耗,以及封装制程转换时的高损耗率等问题上仍有改进空间。为此,台积电采取“先易后难”的推进策略,计划待未来光罩尺寸技术逐步突破后,再进一步提升基板规格。

作为以面板制造起家的企业,群创也已强势切入FOPLP封装赛道。依托既有3.5代面板产线,群创可直接复用部分生产设备,通过设备折旧摊提有效降低初期投入成本;同时,其封装基板尺寸可容纳相当于6.9片12英寸晶圆的面积,能实现更大批量的同时处理,显著降低单位封装成本。

群创董事长洪进扬透露,目前FOPLP产品已通过客户验证,计划于2025年进入大规模量产阶段。他看好AI热潮将持续拉动高阶芯片需求,而FOPLP技术在提升大尺寸AI芯片产量、降低生产成本方面的优势,将助力群创与合作伙伴共同满足市场对高阶芯片的需求。

在技术布局上,群创的FOPLP“Chip First”技术可帮助客户大幅缩小晶粒尺寸以降低成本,同时维持高密度I/O脚数,并减少整体封装厚度,能满足手机与移动设备对轻薄化的严苛要求,尤其适用于NFC控制器、音频编解码器、电源管理芯片及通讯芯片等产品的先进封装需求。

根据群创公布的FOPLP制程技术蓝图,其技术推进将分阶段进行:今年率先实现“Chip First”制程的量产;针对中高阶产品的重布线层(RDL First)制程,预计在1-2年内导入量产;而技术难度最高的玻璃钻孔(TGV)制程,将联合合作伙伴共同研发,预计需2-3年时间才能投入量产。

作为全球封测厂商中率先布局FOPLP技术的企业,力成科技早在2016年便启动产线建设,并于2019年实现510×515mm规格的量产落地。

目前,力成位于新竹科学园区的全自动FineLine FOPLP封测产线已于2024年6月进入小批量生产阶段,且已获得联发科电源管理IC的封测订单。据力成执行长谢永达此前透露,经过持续工艺优化,510×515毫米规格产品的良率已大幅超出预期,成功获得客户认可。

力成方面表示,公司面板级扇出型封装产品已启动小量出货,另有重量级客户的高阶产品进入验证阶段——该客户采用2纳米制程的高阶系统单芯片(SoC)搭配12颗HBM(高频宽记忆体)芯片,整体封装成本高达25,000美元,属业界少见的超高价值封装设计。谢永达看好AI世代下异质封装对FOPLP解决方案的需求增长,预计2026—2027年相关技术将进一步扩大量产规模,未来先进封装业务对公司营运的贡献有望逐年提升。

此外,长电科技、通富微电、华天科技等国内三大OSAT巨头也表示公司有FOPLP技术储备,可提供从设计到生产的全流程服务。

从当前行业进展来看,FOPLP技术目前尚未实现大规模放量,核心瓶颈在于良率未达预期与行业标准缺失。与晶圆级封装200毫米、300毫米的统一规格不同,FOPLP的面板尺寸呈现碎片化,510×515mm、600×600mm等主流规格至今未形成共识。这种标准化缺失导致设备工具需定制开发,尤其在面板处理和翘曲控制环节增加了设计复杂度,进而推高规模化成本——正如Nordson专家指出的,尺寸差异已成为制约面板级封装发展的关键挑战,这也使得多数业者暂未大举投入。

事实上,FOPLP技术早在2015年便已出现,但因过渡需投入定制化材料、工艺及设备,且大尺寸面板对翘曲控制、材料一致性要求极高,导致其早期难以普及。

不过AI芯片需求热潮正为FOPLP带来转机。尽管台积电已大幅扩充CoWoS产能,但受封装供应限制,英伟达计划在服务器AI芯片中引入FOPLP技术,日月光等厂商的积极布局也让CoWoS面临竞争压力。

当然,FOPLP推广仍需突破障碍:供应商需在保证产出的同时实现成本大幅下降,才能推动客户从FOWLP转向FOPLP;其作为异构集成灵活平台的潜力,也依赖于面板级基板的成本优化与高良率量产突破。

尽管挑战仍在,但凭借成本优势与设计灵活性,FOPLP已成为扇出型封装领域的重要竞争者,未来发展潜力值得期待。

CoWoP = CoWoS -封装基板?

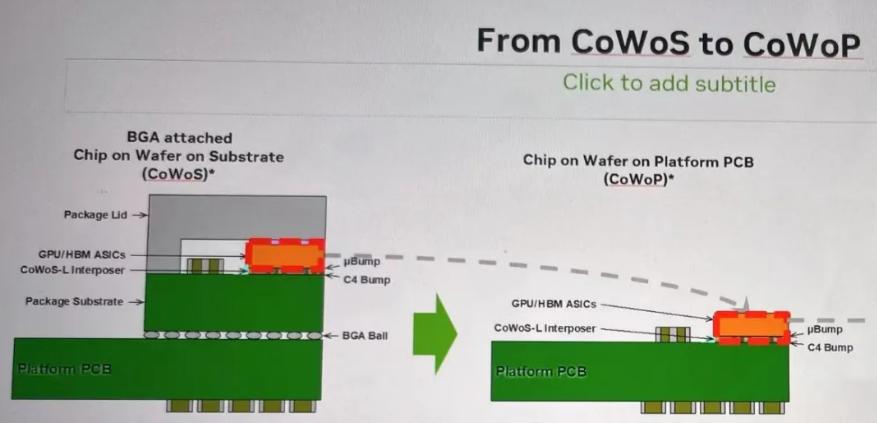

英伟达提出的CoWoP(Chip on Wafer on PCB)是又一种革命性的系统级封装技术,其核心是通过将裸芯片直接通过微凸点倒装到硅中介层上,再与PCB基板键合,实现封装基板与PCB的一体化设计,省去了传统ABF/BT有机封装基板环节。

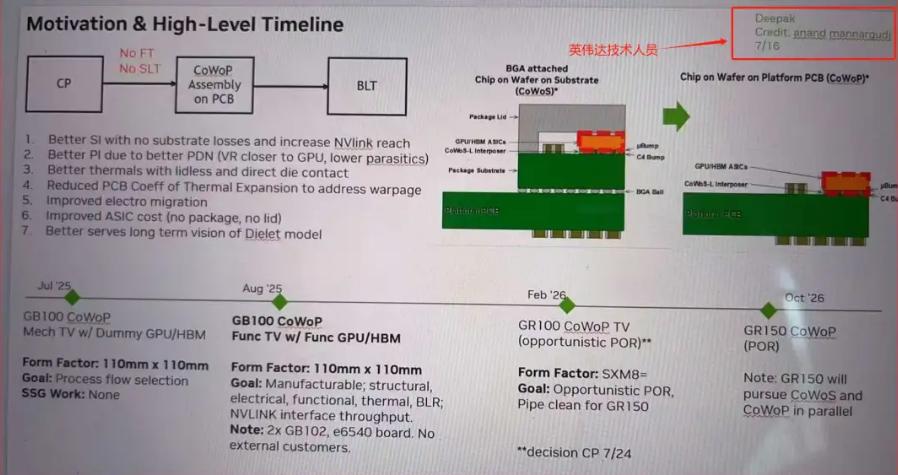

该封装路线图是由英伟达技术人员Anand Mannargudi近日在内部PPT中提出:

可以看到,原来芯片是CoWoS-L封装,通过BGA和PCB连接。而CoWoP把CoWoS-L的载板去掉了,直接通过C4 bump和PCB连接(目前尚不清楚是否能成功连接)。

与当前AI芯片(如H100/H200)标配的CoWoS封装技术相比,CoWoS包含芯片、中介层、封装基板和主板四层结构,层级过多导致信号路径长、功耗损耗大、成本高;CoWoP则移除封装基板和BGA球,简化结构,缩短信号传输距离。

不过需要注意的是,取消封装基板后,主板需具备原基板的高精度布线能力(如微米级线路密度),使“Die-on-Board”组装成为可能。

因此,CoWoP封装技术的优势和挑战不难归纳。

CoWoP作为新兴封装技术,通过重构传统封装架构,在性能、成本、散热等多维度形成显著优势,具体可归纳为以下核心亮点:

- 信号完整性提升:省去了传统封装中的有机基板层级,通过硅中介层与PCB的微凸点倒装互连,实现信号路径大幅缩短,信号传输损耗降低,高带宽连接可靠性显著增强。

- 电源完整性强化:电压调节器(VRM)可集成于更靠近GPU裸片的位置,大幅缩短供电路径,减少寄生电阻、电容和电感等参数。这使得电压稳定性提升,噪声干扰降低,供电响应速度加快,有效改善高负载下的供电效率。

- 热性能优化:采用“无盖设计”(Lidless),散热器可直接接触GPU裸片,配合供电损耗减少带来的产热降低,散热效率显著提升,尤其适配功率超1000W的高端GPU芯片需求。

- 降低翘曲与失配风险:去除热膨胀系数(CTE)差异较大的有机基板,减少热-机械失配问题,显著降低封装翘曲风险,提升结构稳定性。

- 设计灵活性增强:支持高密度布线(可达12层)和弹性化芯片模块整合,推动封装向“无封装架构”长期愿景演进,可实现更薄、更轻、更高带宽的模块设计,适配AI加速卡、光模块(Tb/s级)、汽车电子等高算力场景。

- 成本降低:省去昂贵的ABF/BT有机基板、BGA焊球及封装盖等环节,简化制造流程,不过要改用高性能PCB面板替代,整体制造成本降低情况暂不明晰。

虽然CoWoP拥有诸多优势,但是也存在不少挑战:

- PCB主板技术门坎大幅提高:Platform PCB必须具备封装等级的布线密度、平整度与材料控制,具备过去由封装Substrate提供的高密度布线能力,包括精准微线距、精准信号/电源/地层布线能力,来保证信号完整性与功率分配等,这对PCB的制造工艺和材料要求极高;

- 返修与良率压力剧增:GPU裸晶直接焊接主板,失败即报废,制程容错空间低,良率提升难度大;

- 设计复杂度增加:提升芯片-中介层-PCB三方联合仿真需求,芯片封装厂和下游PCB制造厂必须从设计阶段就深入配合,增加了开发成本和供应链管理难度。

- 技术转移成本高:从CoWoS转向CoWoP需要对整个封装工艺和供应链进行调整,涉及设备、材料、工艺等多个方面,技术转移成本较高。

总之,CoWoP要求PCB与interposer、die一体设计,信号、电源、热管理、机械力学需协同工程化实现,这需要芯片企业、设计工具商、EDA、材料商、PCB厂商和封测厂商重新协作,共研新规范。

CoWoP争议:短期难落地?

据透露,英伟达被曝计划在Rubin Ultra芯片考虑采用CoWoP。目前CoWoP技术已进入实质性验证阶段:2025年7月,英伟达在内部GB100测试平台(搭载Dummy GPU/HBM,尺寸110mm×110mm)启动机械样板测试;2025年8月将完成结构、电气、热性能及NVLink带宽验证;2026年2月开启GR100平台功能验证,计划2026年10月在GR150平台实现CoWoS与CoWoP并行封装策略。

此外,英伟达计划联合台积电、矽品及PCB供应链厂商,于2025年9月研讨450mm×450mm规格CoWoP封装的可行性。

不过需要注意的是,GB100、GR150这些大概都是英伟达的内部工程测试样品,主要是为了进行先进封装技术的研发和技术探索,并不一定会商品化对外销售。

英伟达在CoWoP技术上的规划与影响,业界有声音表示:“CoWoP技术若顺利落地,将推动主板成为芯片‘最后一层封装’,不仅能降低整体成本,更有望主导AI硬件平台定义权,甚至重构产业竞争格局。”

CoWoP看似是“CoWoS减去封装基板”的简单减法,实则是技术飞跃——要求PCB主板具备封装基板级的高精度布线能力,这一变革正重塑产业链价值逻辑。

不难理解,英伟达将竞争从“芯片维度”提升至“系统维度”,通过“芯片+封装+主板”三位一体的系统级平台构建护城河,定义AI硬件标准,甩开竞争对手;台积电凭借硅中介层核心技术,从CoWoS的“参与者”升级为“系统集成核心”,绑定度进一步加深。另外,云巨头或有能力跟进,但AI芯片初创企业难以承担重资本的系统级创新。

若CoWoP技术成熟,将触发封装、基板、PCB、服务器ODM等下游产业链的价值重构与技术洗牌,跟不上节奏的企业可能被甩出AI算力新赛道。

不过也有PCB业者指出,传统载板技术成熟且价格稳定,CoWoP的替代进程仍需时间积累。

摩根士丹利在其最新研报中指出,英伟达短期内大规模采用CoWoP技术的可能性极低,下一代GPU产品Rubin Ultra仍将沿用ABF基板方案,且其基板规格较前代更大、层数更多,与CoWoP技术路径相悖。

对于短期内CoWoP技术应用受阻的核心原因,摩根士丹利指出3点原因:

- 技术壁垒显著:CoWoP要求PCB线宽/线距(L/S)缩小至10/10微米以下,与ABF基板标准相当,但当前高密度互连(HDI)PCB的L/S为40/50微米,即使是高端类基板PCB(SLP)也仅达20/35微米,从20/35微米向10/10微米突破存在巨大技术难度。

- 切换风险高企:台积电CoWoS良率已接近100%,在此基础上切换技术将引入不必要的良率风险;同时,技术转换涉及供应链生态重组,而Rubin Ultra计划一年内量产,短期内完成转换在商业逻辑上并不合理。

- 依赖惯性难破:技术转换的复杂性与供应链重构成本,使得英伟达对ABF基板的依赖短期内难以改变。

尽管短期应用受限,但大摩研报认为英伟达可能将CoWoP作为长期研发项目并行推进,其潜在价值包括:解决基板翘曲问题、扩展PCB上NVLink覆盖范围、提升散热效率(无需封装盖)、缓解特定封装材料的产能瓶颈,以及简化GPU板制造工艺。

报告强调,短期内ABF基板供应商地位稳固,而CoWoP若长期落地,可能推动SLP供应商崛起,同时对传统ABF基板厂商形成潜在冲击。

总体而言,CoWoP的技术优势值得关注,但短期内仍难以撼动现有封装技术格局。而英伟达作为行业领导者,在新技术尚未100%成熟时,保留成熟方案作为“安全网”,确保其产品迭代和市场供应不会因技术风险而中断。

写在最后

在AI算力需求爆发的浪潮下,CoWoS封装技术虽曾凭借高集成优势成为行业核心,但工艺复杂、成本高昂及产能瓶颈等问题日益凸显,推动业界加速探索替代方案。

台积电主导的CoPoS通过面板基板替代硅中介层,突破封装尺寸限制,计划2028年后量产,成为CoWoS的长期演进方向;FOPLP凭借成本低、灵活性强的特点,吸引日月光、三星、群创等巨头布局,虽因良率与标准缺失暂未放量,但在AI大尺寸封装需求驱动下潜力显著;而英伟达提出的CoWoP技术通过简化架构提升性能与成本优势,却因PCB技术壁垒、切换风险等短期内或难以落地,更多作为长期研发方向。

整体而言,当前行业处于“成熟技术稳支撑、新兴技术谋突破”的格局,CoWoS仍居主导,而CoPoS、FOPLP、CoWoP等技术在巨头推动下加速迭代。未来,随着技术成熟与标准统一,先进封装领域将迎来价值重构,在创新与稳定的平衡中支撑AI算力持续增长。