并排放置 SoC 与内存,消息称三星探索为 Exynos 芯片导入 FOWLP-SbS 先进封装

2025-12-30

/ 阅读约2分钟

来源:IT之家

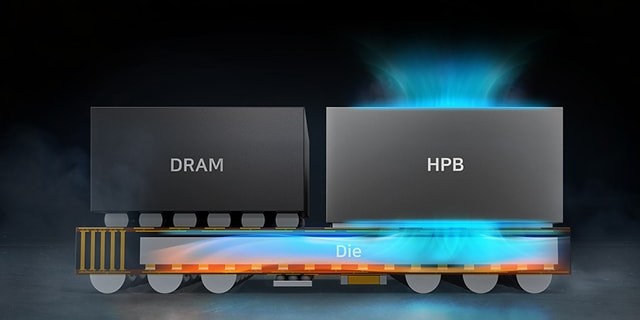

三星电子开发FOWLP-SbS封装技术,有望提升Exynos芯片散热能力,SoC Die和DRAM并排放置,覆盖HPB散热结构,增强散热效能,预计率先用于折叠屏产品。

IT之家 12 月 30 日消息,韩媒 ZDNET Korea 当地时间今日报道称,三星电子正在开发一项名为 FOWLP-SbS(IT之家注:SbS 即 Side-by-Side,并排)的先进封装技术,有望进一步提升 Exynos 芯片的散热能力。

现代的高端移动端处理器(如 Exynos 2600)通常是在 SoC Die 逻辑芯片上集成封装 DRAM 内存,便利走线的同时能缩减占地面积。Exynos 2600 还在 SoC Die 上引入了 HPB 散热结构,将热阻降低了多达 16%。

而在采用 FOWLP-SbS 封装的芯片上,SoC Die 和 DRAM 并排放置,上面覆盖 HPB,此举有利于扩大 SoC Die 和 HPB 的接触面积,进一步增强散热效能。SoC Die 与 DRAM 预计将采用混合键合技术实现短间距高效互联。

韩媒认为,FOWLP-SbS 可降低封装成品厚度,支持更厚的 SoC Die、DRAM,有利于供电线路的设计优化,但也有着面积占用更大的劣势,预计其会率先用于重视厚度的折叠屏但平面空间相对充足的折叠屏产品上。