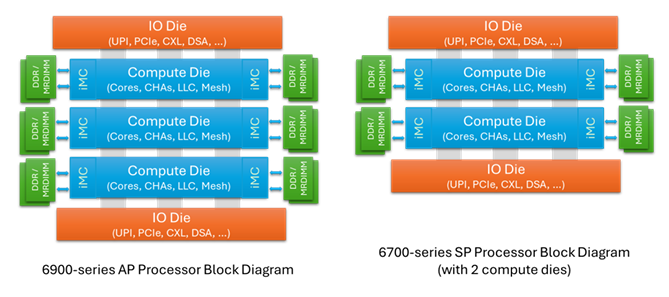

IT之家 1 月 4 日消息,英特尔最新提交的 Linux 内核代码证实,下一代 Diamond Rapids 至强处理器将采用全新的模块化设计,搭载 CBB 计算芯片与 IMH I/O+ 内存控制器芯片。

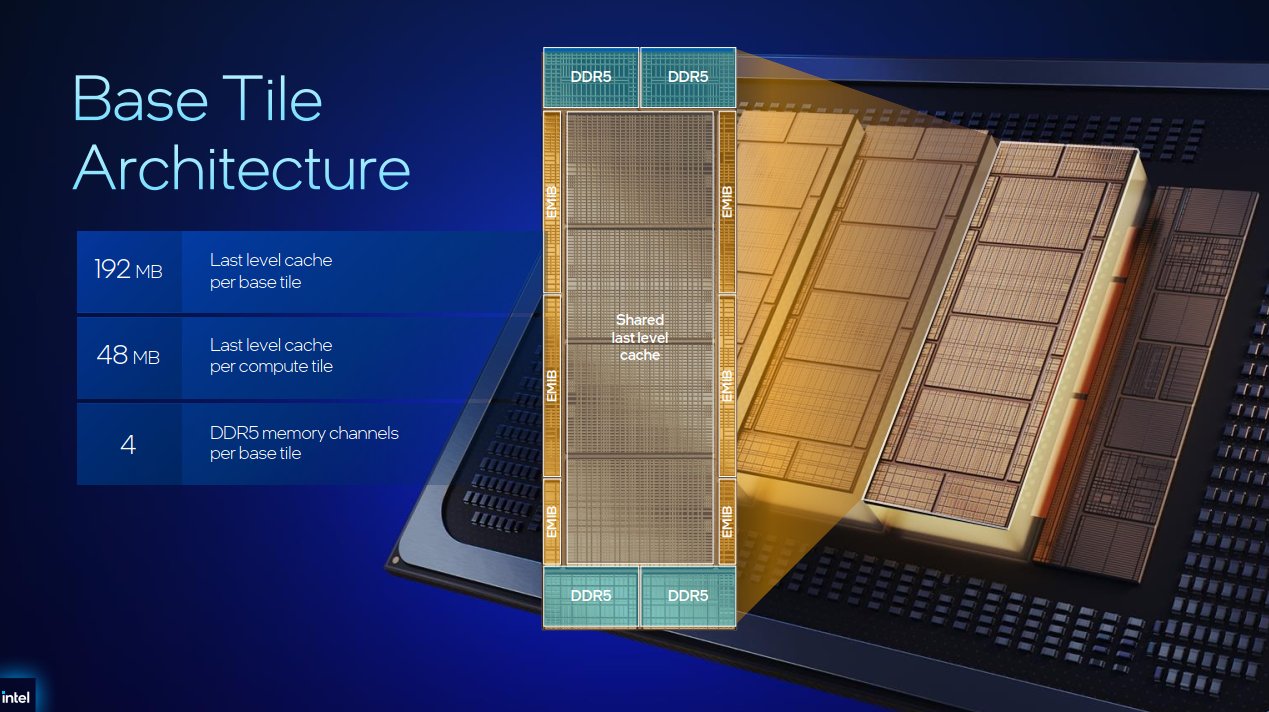

与集成了内存控制器的 Granite Rapids 不同,Diamond Rapids 将把内存控制器分离出去,意味着计算与 I/O、内存子系统在物理层面上实现了更彻底的分离。

其中,CBB 即核心计算模块(Core Building Block),而分离出去的内存控制器将分配于全新的 IMH(Integrated I/O & Memory Hub)芯片上。

@InstLatX64 爆料显示,Diamond Rapids 最多可包含两个这样的 IMH 芯片。他还指出,IMH 芯片将置于基板上,其布局类似于英特尔此前在 Clearwater Forest 架构中的设计。

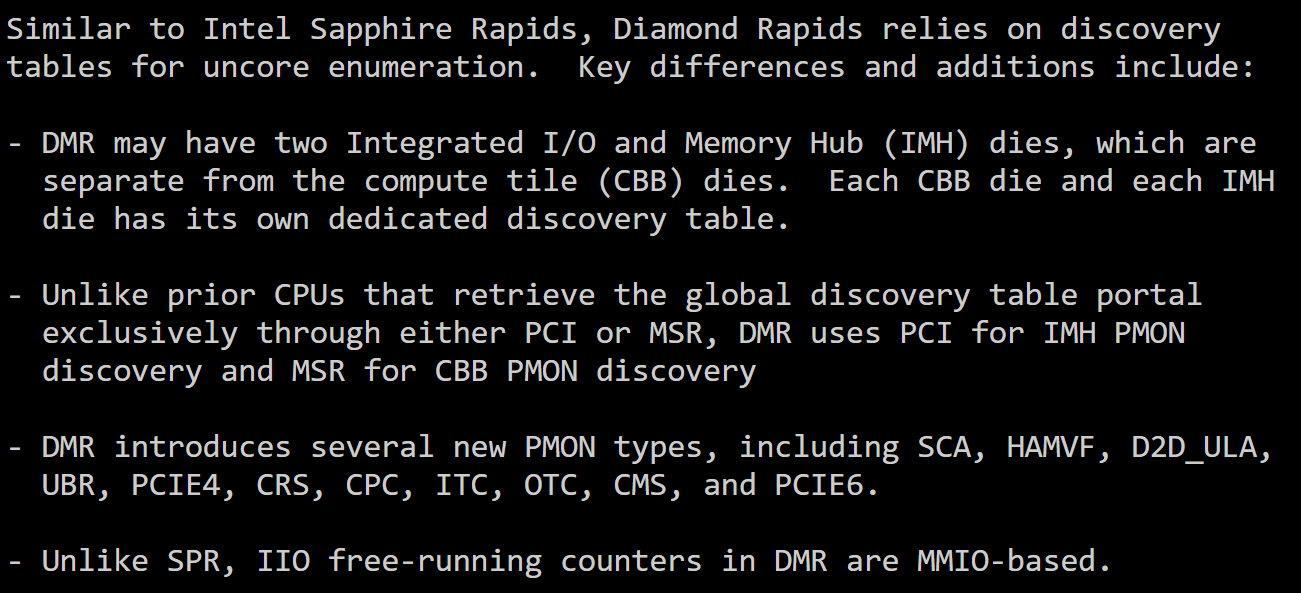

与英特尔 Sapphire Rapids 类似,Diamond Rapids 依然依赖“发现表”进行枚举。关键区别与新增内容在于:

Diamond Rapids 可集成两个 I/O 与内存中心芯片,它们与计算芯片是分离的。每个 CBB 芯片和每个 IMH 芯片都拥有各自独立的“发现表”。

与此前 CPU 仅通过 PCI 或 MSR 检索全局“发现表”门户不同,Diamond Rapids 可使用 PCI 进行 IMH 性能监控发现,而 CBB 则通过 MSR(模型特定寄存器)完成。

Diamond Rapids 还新增了多种 PMON 类型,包括 SCA、HAMVF、D2D_ULA、UBR、PCIE4、CRS、CPC、ITC、OTC、CMS 和 PCIE6。

与 Sapphire Rapids 不同,Diamond Rapids 在 IIO 自由运行计数器的实现方式上将从以往的方式转向基于 MMIO 的方式。

除此之外,Diamond Rapids 还将添加对 PCIe Gen6 的支持。这也符合技术发展趋势,该标准将在今年应用于 Diamond Rapids 和 Venice 等下一代数据中心平台。

结合此前爆料信息,英特尔 Diamond Rapids 预计最多拥有 192 个核心(甚至有传言指向 256 核),已知这些芯片预计将采用最新的 18A 制程节点,核心架构将采用 Panther Cove(性能核)。

早期信息显示,在支持多路配置的 LGA 9324 平台上,其 TDP 最高可达 650W。英特尔预计在 2026 年中期或下半年发布 Diamond Rapids 处理器。IT之家后续将保持关注。