可选当前最先进工艺:消息称三星电子正开发 4~2nm 定制 HBM 基础裸片解决方案

2026-01-21

/ 阅读约2分钟

来源:IT之家

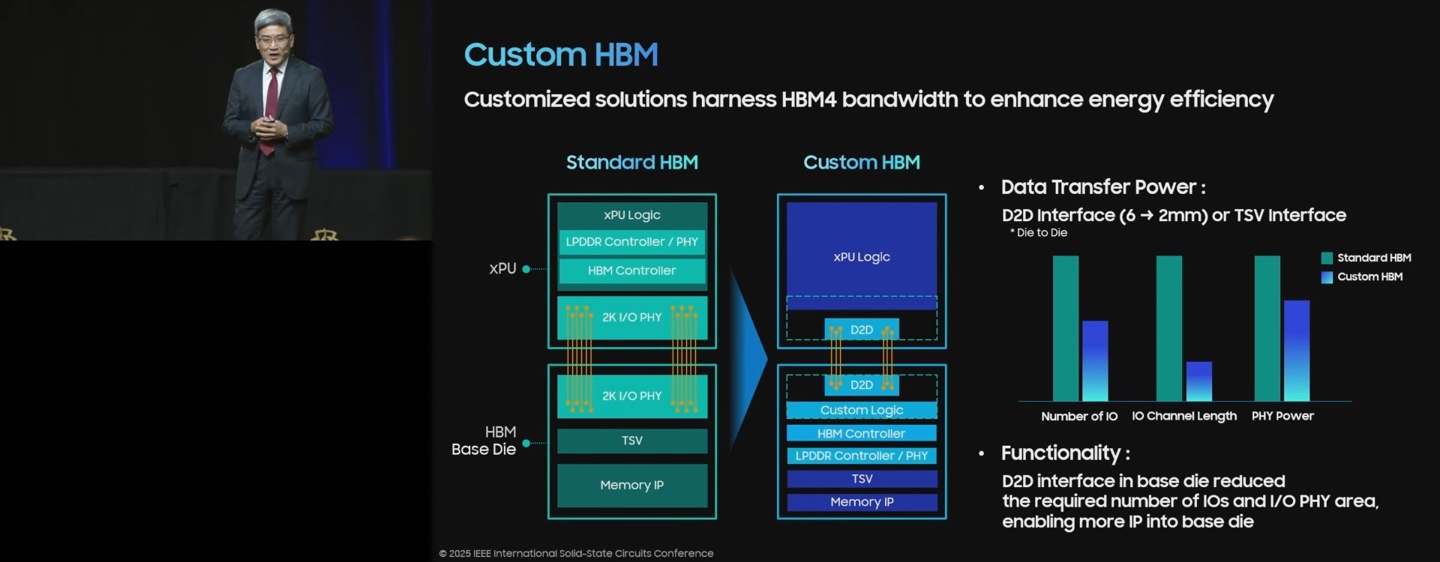

三星电子将在HBM4后的定制HBM内存上延续制程优势策略,提供4nm至2nm基础裸片解决方案。HBM基础裸片可承载XPU电路功能,工艺越先进,容纳逻辑电路越多,能效越出色。

IT之家 1 月 21 日消息,韩媒 ZDNET Korea 今日报道称,三星电子将在 HBM4 后的定制 HBM 内存上延续“制程优势”策略,提供从 4nm 直到当前最先进的 2nm 的一系列基础裸片 (Base Die) 解决方案。

IT之家注:台积电则计划为定制 HBM 基础裸片导入 N3P 制程。

搭配 HBM 内存的高阶 AI XPU 芯片正面临单体芯片理论最大面积(858mm² 的光罩尺寸)限制算力进一步提升的情况,化解这一问题的方式除了多芯片的物理 / 通信互联外还包括将部分电路卸载到邻近的 HBM 基础裸片上。

由于 HBM 内存进入 HBM4 后,HBM Base Die 也采用逻辑半导体制程,因此可承载原应由 XPU 主体负担的电路功能。而 HBM Base Die 工艺越先进,其就越能容纳逻辑电路、能效越出色。

内部人士表示,三星电子的定制 HBM 基础裸片解决方案由系统 LSI 业务新设立的定制 SoC 团队负责。