硅光子技术正在改变数据中心,而最大的变革还在后面。

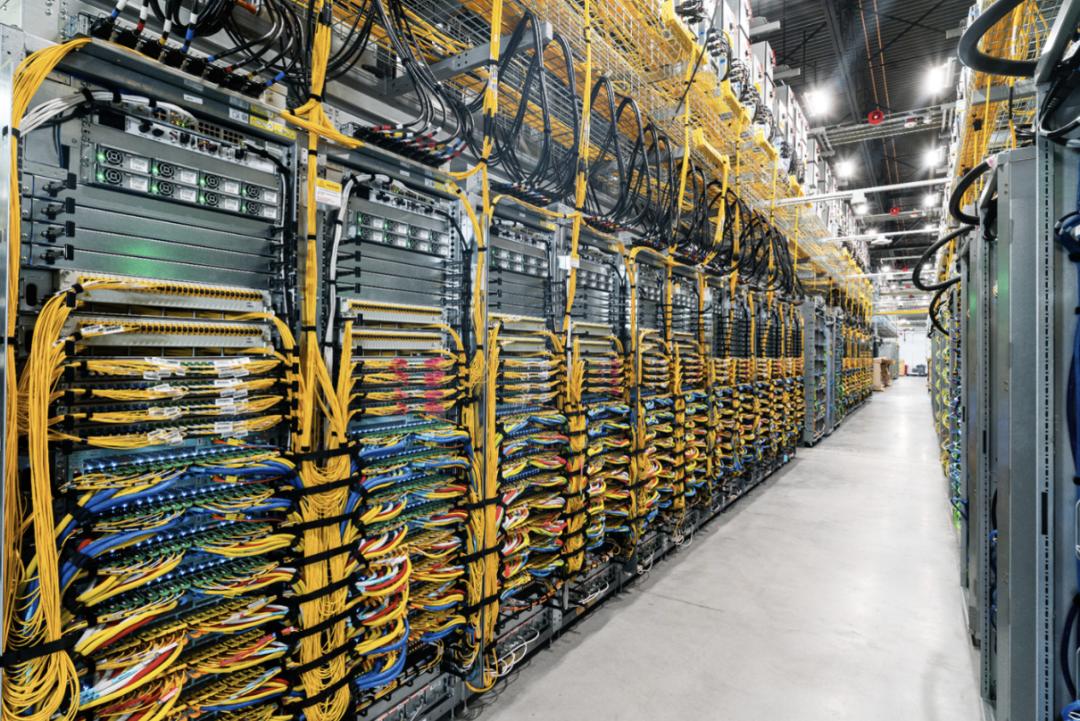

可插拔光模块已在数据中心应用多年,并主导着横向扩展连接。下图是谷歌的 Jupiter 网络,用于互连集群中的数千个 Ironwood TPU。图中大部分线缆为黄色,代表单模光纤 (SMF)。至于纵向扩展,英伟达 CEO 黄仁勋去年夏天曾表示,“我们应该尽可能长时间地使用铜缆。” 大多数观察人士认为,最多还能再用两到三代。

图 1:Google Jupiter 网络

横向扩展(scale-out )网络中存在大量连接。每个机架都配备一个机架顶部 (TOR)以太网交换机,拥有 128 个以上的端口,其上方还有 1-2 层横向扩展网络。纵向扩展(scale-up )的链路数量则要多得多。例如,在 Nvidia NVL72 机架中,有 18 个交换机,每个交换机直接连接到 72 个 GPU 中的每一个:18 x 72 = 每个机架 1296 个链路。随着 NVL144 和 NVL576 等更大规模的 pod,每个机架的纵向扩展链路数量也会增加。因此,当纵向扩展采用光纤时,光纤市场将会大幅增长。

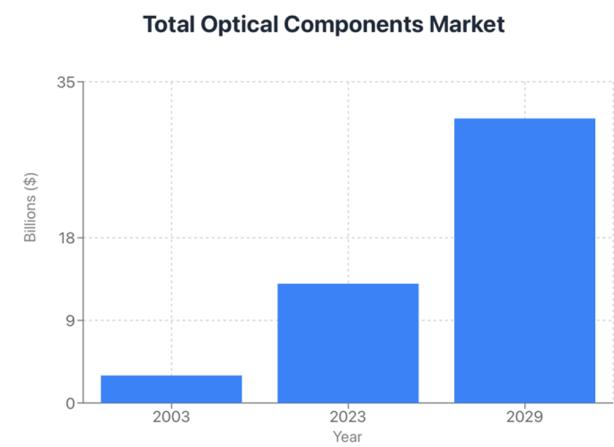

在2025年光纤通信展(OFC 2025)上,OMDIA发布的光纤器件市场预测显示,市场规模已从2003年的数十亿美元(主要应用于电信领域)增长到2023年的约130亿美元,此后增长速度将显著加快,预计到2030年将达到250亿美元,这主要得益于人工智能网络的发展。首先是横向扩展,几年后是纵向扩展。CignalAI最新的预测则认为,到2029年,市场规模将达到310亿美元。

图 2:光器件市场总规模

光学元件包括:

硅光子学是将原本分散的光子器件集成到改进的CMOS工艺中;

激光器、硅光放大器(SOA)以及其他基于III-V族工艺(如磷化铟(InP)和砷化镓(GaAs))制造的器件,以及封装、光纤、连接器、适配器,用于在芯片之间提供连接。

本文重点介绍硅光子学。后续文章将讨论其他关键组件。

光如何在芯片间传输数据

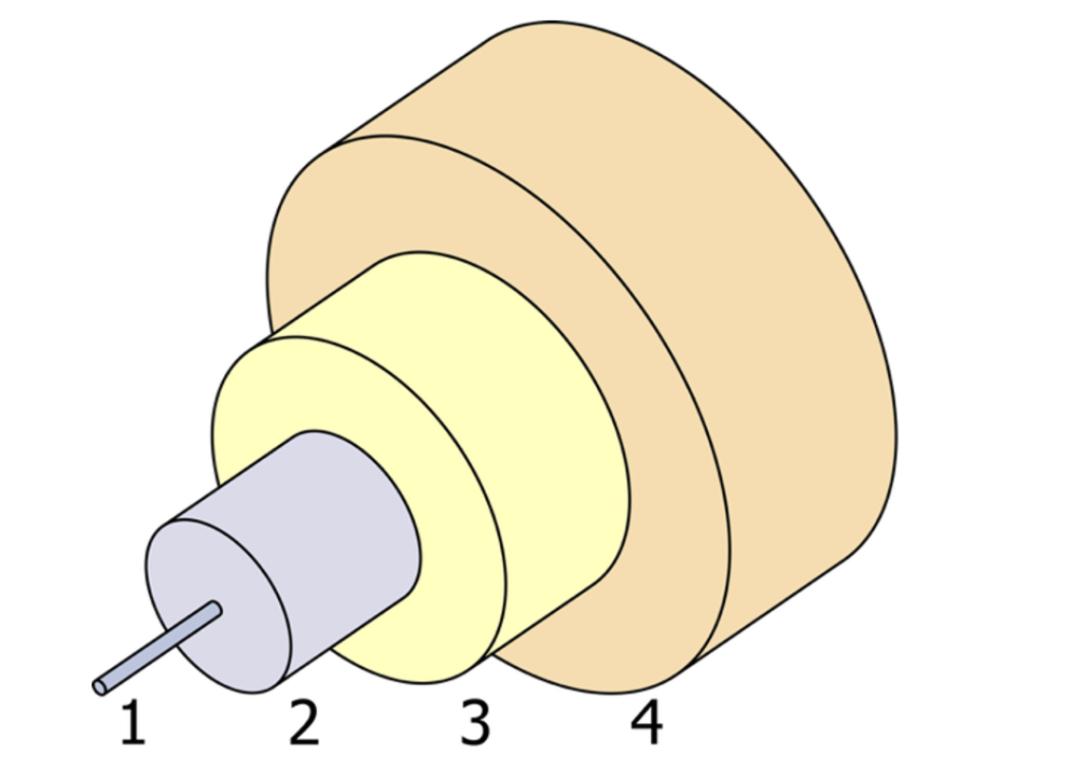

数据中心的铜缆正在向光纤过渡。实际的物理光连接由光纤电缆实现,这些电缆通常是“单模光纤”,用于传输单模或多波长的光。包层可以保护光纤,但更重要的是,包层的折射率低于纤芯,从而使光线集中在光纤中。光纤电缆市场规模庞大。市场领导者康宁公司每年销售价值 68 亿美元的光纤产品。Meta 公司最近与康宁公司达成了一项价值 60 亿美元的协议,将在未来几年内继续供应光纤电缆。

图 3:单模光纤电缆——实际光纤直径为 8-9毫米,电缆直径为 2-3 毫米

实际的光纤由玻璃制成,极其纤细——只有9毫米,也就是1/100毫米。如此细小的直径使得光保持单模状态,而硅光子学正是利用了这一点。

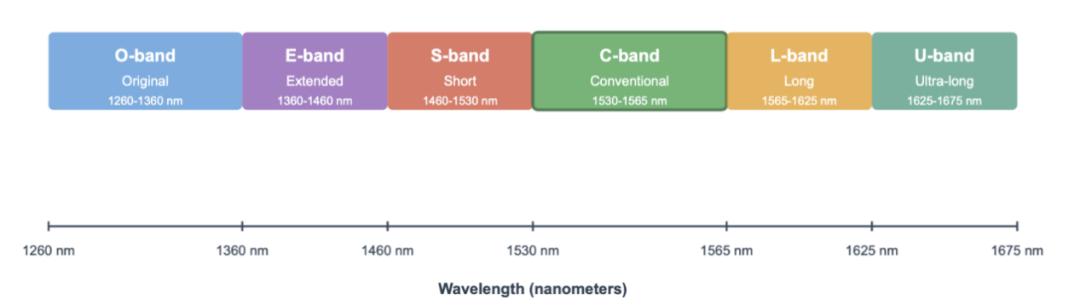

光纤通信中使用的波长是O波段、E波段、S波段、C波段和L波段,因为这些波段在光纤中的信号损耗相对较低。它们都位于红外光谱范围内。

图 4:光纤中的光传输频段

由于 O 波段在硅波导中的传输损耗低,因此被应用于硅光子学领域。

在光纤或芯片的波导中,可以使用单波长或多波长信号。多波长信号可以通过两种方式实现:粗波分复用 (CWDM) 和密集波分复用 (DWDM)。CWDM 指的是波长之间的间隔相对较大;DWDM 指的是波长之间的间隔相对较小。CWDM 和 DWDM 都能提供更高的带宽,但它们的实现挑战各不相同。

请注意,尽管几乎所有用于互连的光纤都是 SMF(单模光纤),但它们不一定可以互操作,因为光可以在单个或多个波长、不同波长和/或使用不同的连接器上传输。

硅光子学应用

可插拔光器件

硅光子学目前在数据中心市场的主要驱动力是可插拔光收发器。

它们是一种标准化的热插拔设备,一端连接到交换机或服务器的电气接口,另一端连接到光纤。与它们所取代的铜缆相比,它们能够以更高的带宽和更低的功耗,通过光纤将数据从一个交换机/服务器高速传输到另一个交换机/服务器。

可插拔光收发器的主要组件包括:1)激光器;2)具有DSP功能和高速SerDes的CMOS芯片;以及3)硅光子芯片。在这些收发器中,硅光子调制器(通常为马赫-曾德尔调制器)对激光进行调制,以叠加来自CMOS芯片的数据。此外,还有滤波器、耦合器、石榴石、透镜和隔离器。所有这些组件都封装在标准化的可插拔封装中。

Coherent 的 2025 年投资者报告预测,可插拔光器件市场将从 2023 年的 60 亿美元增长到 2030 年的 250 亿美元!到 2030 年,市场将主要以1.6T(1.6 太比特/秒)和 3.2T 数据速率为主,一些速度较慢的传统产品仍将继续出货。

光路交换机 (OCS)

谷歌多年来一直在谷歌云中使用光路交换机 (OCS) 。

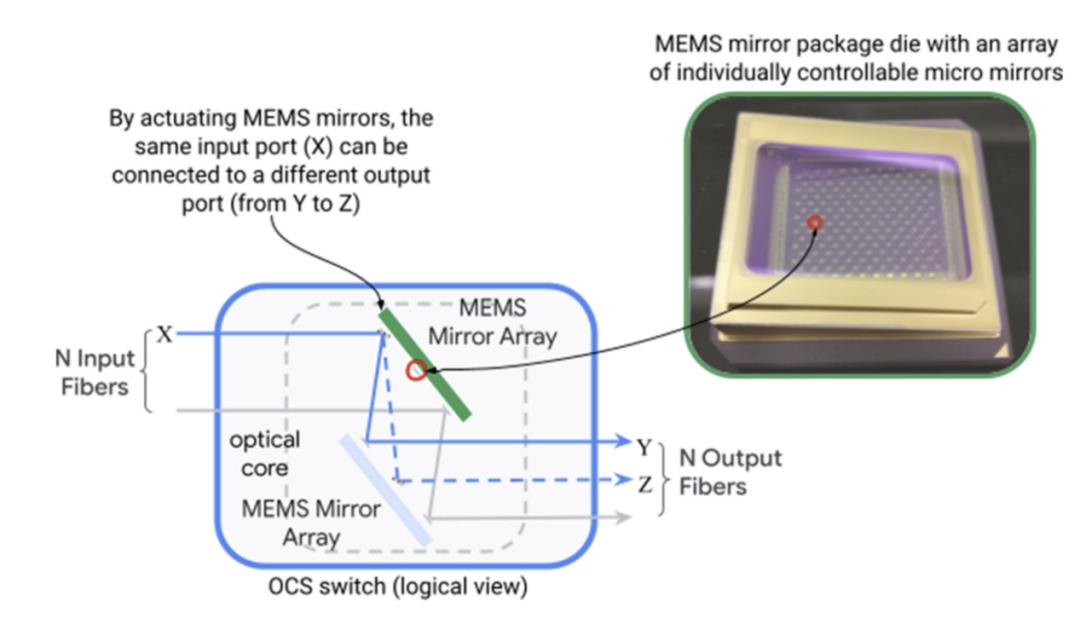

与其他AI加速器不同,谷歌的TPU无需交换机,采用三维路由结构,可实现数千个TPU组成的集群。其机架顶部(TOR)交换机使用可插拔光模块,并连接到OCS层,从而实现整个数据中心顶层互连的重新配置。这对于冗余、可靠性和应对不断变化的工作负载的网络重配置至关重要。谷歌的方案采用MEMS(微机电系统)镜,这些微镜可接收数百根输入光纤,并将光路导向数百根输出光纤中的任意一根。

图 5:Google OCS 使用 MEMS 镜像来路由/切换灯光

Lumentum 和 Coherent 目前也提供 OCS 技术,分别采用 MEMS(Lumentum)和液晶(Coherent)。在 2025 年 12 月的一次金融会议上,Coherent 的首席执行官表示:“我们非常看好 OCS。”去年夏天,他们预测 OCS 的潜在市场规模 (TAM) 将超过 20 亿美元,但现在看到客户兴趣日益浓厚,应用领域也更加广泛,因此他们将 TAM 的预估上调至超过 30 亿美元。

多家初创公司正在利用更紧凑的硅光子技术开发“二维”光通信系统(OCS)。这些公司包括 iPronics、nEye 和 Salience。它们都在进行概念验证样品测试(nEye 和 Salience)或交付首批产品(iPronics)。这些技术最终可能比现有架构更经济或更可靠。这些高密度解决方案也可能使 OCS 能够应用于横向扩展连接,首先用于冗余/可靠性,然后用于全 GPU 到全 GPU 的 OCS 连接,甚至有一天可能取代硅分组交换机来实现横向扩展。

共封装光学器件 (CPO)

CPO可实现比可插拔光学器件更高的密度和更低的功耗。

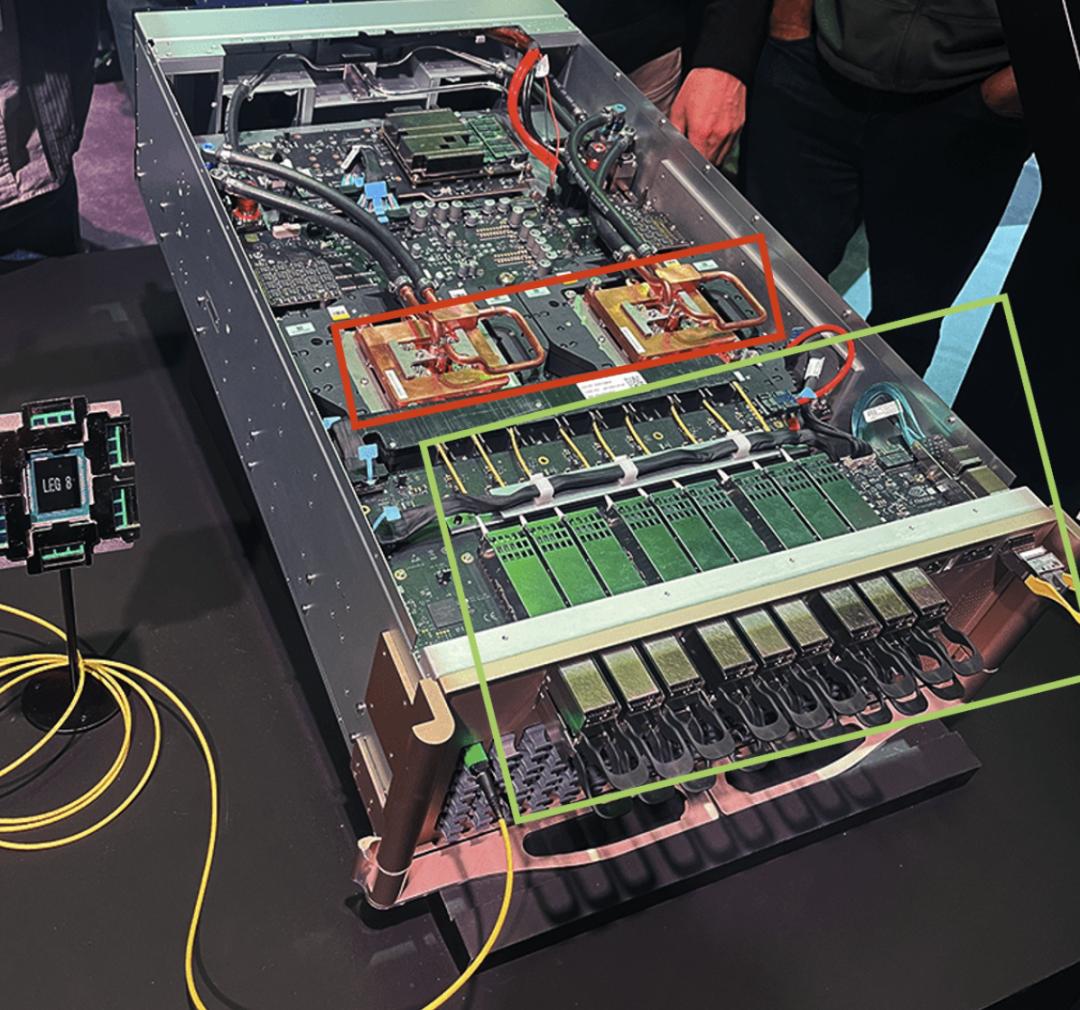

随着英伟达和博通宣布将于 2025 年推出采用共封装光器件的以太网横向扩展交换机以降低交换功耗,CPO 已开始蚕食可插拔交换机的市场份额。

图 6:Nvidia Spectrum-X 横向扩展交换机(含 CPO)

交换机是两个芯片(上图中红色方框内),上方覆盖着液冷外壳。从顶部伸出的四根粗黑电缆是液冷进出线。可插拔激光器(上图中绿色方框内)位于图片底部盒子的顶部,用于提供信号载波。共有9个激光器,每个盒子可能包含8个激光器。可以看到9根黄色电缆从激光器连接到交换机芯片。激光器采用可插拔设计是因为它们的故障率较高,这样在发生故障时可以轻松更换,而无需更换整个交换机。左下角仅连接了一根输入光纤——即黄色电缆。可以看到还有许多其他光纤连接器。从I/O面板到芯片的光纤连接必须位于我们看不到的下方。

CPO(可插拔式)的节能优势(仅为可插拔式的三分之一)对于规模化应用而言意义重大,因为每个机架通常有超过1000个连接。Nvidia、Broadcom、Ayar Labs、Celestial(最近被Marvell收购)、Lightmatter和Ranovus都在致力于开发CPO解决方案。

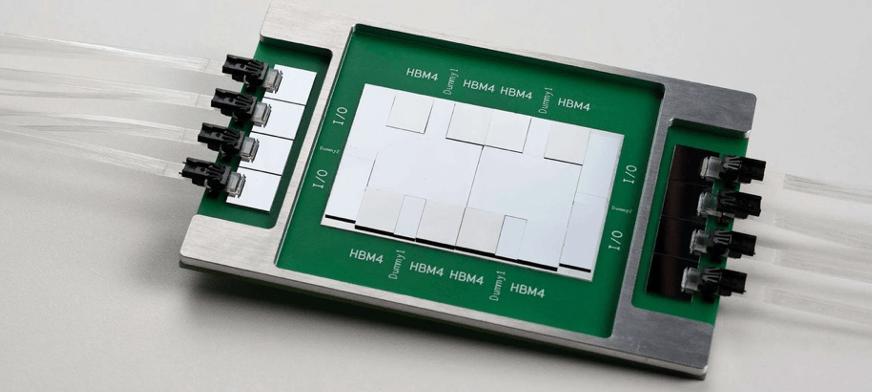

图 7:配备 CPO 的 AI 加速器示意图

如今,所有GPU/XPU/AI加速器都使用铜缆连接。正如英伟达的黄仁勋所指出的,目前的趋势是尽可能长时间地使用铜缆。但铜缆的性能提升已接近收益递减的瓶颈,更高的性能会导致连接距离过短,从而增加错误率。光纤连接将使AI加速器能够以更低的延迟和更大的芯片容量,持续提升互连带宽。

Ayar Labs 与 Alchip 于去年底展示了基于 CPO 的 AI 加速器概念图。加速器和 HBM 芯片位于硅中介层上,而光引擎芯片(图中展示了 8 个,包含超过 256 根光纤)则安装在有机基板上。未来,光引擎将直接安装在中介层上。

硅光代工,大有可为

与CMOS相比,目前的硅光子制造规模较小,但硅光子器件代工厂将迎来巨大增长,台积电或将成为第一。

目前主要的硅光子芯片代工厂商是GlobalFoundries(最近收购了AMF)和Tower Semiconductor。此外还有一些规模较小的厂商,例如提供原型制作服务的imec、荷兰的LioniX以及马来西亚的Silterra。台积电、三星和联电都在为其代工产品开发硅光子芯片技术。

GlobalFoundries (GF)收购 AMF 后,声称已成为全球排名第一的硅光子(SiPho)代工厂,预计 2026 年 SiPho 收入将接近 3 亿美元,到本十年末将超过 10 亿美元。GF 硅光子副总裁兼总经理 Kevin Soukup 说,他们在新加坡拥有两座晶圆厂,主要专注于 C 波段和 L 波段,主要用于长途相干应用。其中一座是他们收购的 AMF 晶圆厂,另一座是他们原有的规模更大的晶圆厂,该晶圆厂也采用 AMF 工艺。利用更大的晶圆厂,他们可以大幅提升产能,满足长途客户的需求。

在马耳他,他们的 SiPho 晶圆厂专注于可插拔收发器和共封装光学器件。他们拥有一种可以在芯片上制造 45nm CMOS 以及射频和/或硅光子器件的工艺。他们还可以制造不含 CMOS 的 SiPho 芯片。他们利用其12nm FinFET工艺的先进设备来制造低损耗波导。他们还拥有类似于台积电COUPE工艺的技术,该工艺将电接口芯片(EIC)与光子集成芯片(PIC)集成到单个芯片中。他们支持光纤输入的边缘连接和顶部连接,但与COUPE不同的是,他们使用光学反射镜进行顶部连接,将光反射90度角至边缘连接,从而无需使用光栅耦合器。这使他们在宽带领域具有优势,因为光栅耦合器难以处理宽带信号。Soukup表示,他们的客户已在设计中“集成”了GF的CPO技术,以实现横向扩展和纵向扩展。

GF还预测,2026年全球排名第二的硅磷晶圆代工厂营收约为2亿美元,第三约为1亿美元,第四约为5000万美元。将这三家工厂的营收相加,并估算其余工厂的营收,2026年硅磷晶圆代工厂的总营收将不足10亿美元/年。这不到台积电年营收的1%。

Tower Semi 似乎是全球第二大硅光子器件代工厂。据介绍,Tower Semiconductor 的 PH18 SiPho 晶圆代工方案旨在满足日益增长的 O 波段和 C 波段数据中心互连市场需求。该平台由 Tower Semiconductor 位于美国加利福尼亚州纽波特比奇的 200 毫米晶圆厂提供。我们、、公司便捷的多项目晶圆 (MPW) 穿梭测试计划可提供低成本的快速原型制作服务。

与其他仅面向特定客户或仅限于小批量原型制作的“封闭式”工艺不同,Tower Semiconductor 的“开放式”平台面向所有 SiPho 客户开放。Tower Semiconductor 业界领先的设计平台,专为光网络和数据中心互连应用而设计。SiPho 工艺与公司的 SiGe BiCMOS 工艺相辅相成,通过提供高速电子器件以及光器件,为不断扩展的数据通信市场提供更完整的解决方案。

值得一提的是,在2024年,Tower推出了全新的300毫米硅光子(SiPho)工艺,并将其作为标准代工产品。据介绍,这项先进工艺是对Tower成熟的200毫米(PH18)平台(目前已实现量产)的有力补充,为客户提供了一款尖端解决方案,旨在满足下一代数据通信应用中日益增长的高速数据通信需求。

这款独特的 300mm 晶圆采用业内一流的硅波导和最先进的低损耗氮化硅波导技术。更大的晶圆尺寸增强了与行业标准 OSAT(外包半导体封装测试)平台的兼容性,从而有助于与电子元件无缝集成,并提高整体效率。

除了上述两家公司以外,有些公司自行生产硅光子器件,例如英特尔和意法半导体。许多其他半导体/系统公司销售的硅光子产品则由代工厂生产——例如,思科使用格罗方德(GlobalFoundries)的产品。

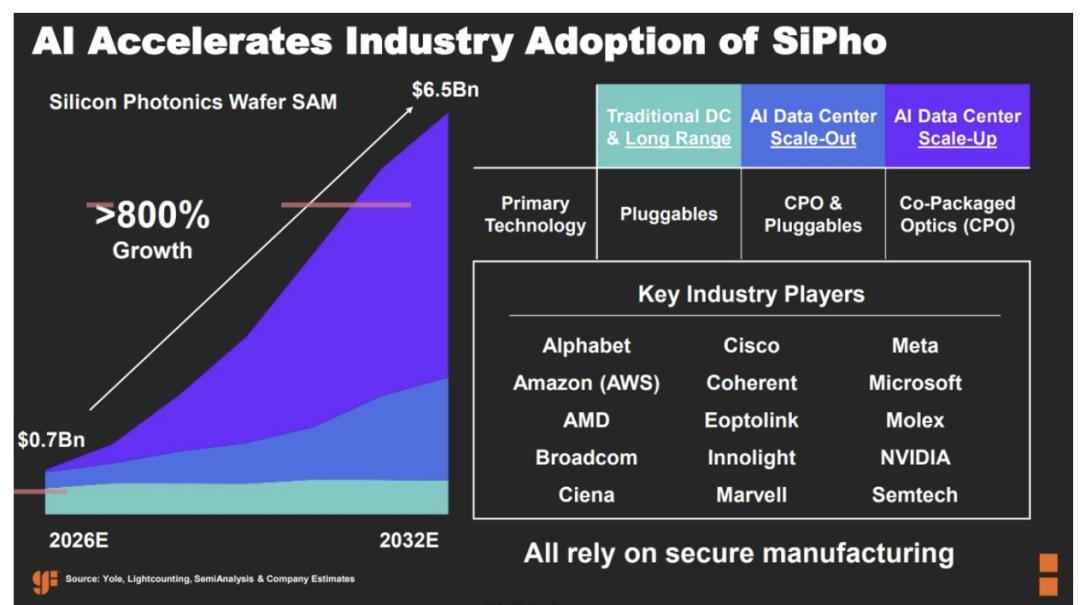

图 8:硅光子晶圆收入预测

数据中心人工智能正推动硅光子代工厂实现迅猛增长:从2026年到2032年,短短六年间增长八倍。目前,横向扩展是主要驱动力。几年后,纵向扩展将成为最大驱动力,因为数据中心纵向扩展涉及的环节远多于横向扩展。

硅光子芯片的市场价值在出售时将远高于芯片本身,因为封装成本可能与芯片成本相当,且利润率超过50%。DataM Intelligence预测,到2031年,硅光子集成电路市场规模将达到320亿美元;Precedence Research预测,到2034年将达到290亿美元。

横向扩展(Scale-out)已开始向可插拔光器件(CPO)过渡,而纵向扩展(Scale-up)在不久的将来也需要CPO。纵向扩展需要CPO,是因为光子集成电路(PIC)必须足够小,才能在GPU边缘集成多个PIC,并且每个PIC都需要大量的光纤连接。这就要求PIC中的关键电路小型化,尤其是调制器,通常采用微环调制器,而不是可插拔光器件中使用的体积更大的马赫-曾德尔调制器。横向扩展转向CPO的原因是,其功耗比可插拔光器件低2/3:网络传输中节省的每一瓦功耗都可以用于计算,从而带来收益。

台积电目前几乎为英伟达、AMD、谷歌、AWS 等公司生产所有 AI 加速芯片。这些芯片由众多芯片组(GPU/XPU、HBM、I/O)组成。台积电要求封装内的所有芯片组都必须由台积电按照其PDK(工艺开发套件)和规范生产,以确保正常运行和高良率。这意味着台积电集成的所有硅光子芯片组都将由台积电生产。一段时间以来,台积电一直在开发其COUPE工艺。很可能,他们开发这项工艺是为了响应其最大客户英伟达和博通的需求,这两家公司都已于去年开始在其横向扩展交换机中部署 COUPE 工艺。

鉴于 a) 硅光子晶圆代工收入增长 8 倍需要巨额资本支出; b) 台积电目前生产 AI 加速器中所有非 HBM 芯片,未来五年内,随着 AI 加速器向 CPO 过渡,台积电很可能从硅光子领域的零基础跃升为全球第一的硅光子晶圆代工厂。日月光等公司拥有一定的 CoWoS 产能,因此可能会出现一些非台积电生产的有机衬底 CPO 产品。或者,格芯或其主要客户可能会说服台积电使用格芯制造的光学引擎芯片——格芯目前最先进的制程节点为 12nm,因此在 AI 加速器领域对台积电并不构成竞争威胁。

硅光子器件、设计和芯片

CMOS 设计师通常会使用包含大量规则和公式的 1000 页 PDK(产品开发工具包)。这些 PDK 包括代工厂提供的多个器件库(只要遵循这些规则,这些器件就能协同工作),以及许多构成完整子系统的大型复杂 IP(知识产权)。

如今的硅光子学就像上世纪80年代的硅设计一样,当时晶圆厂的文档有限,只能用环形振荡器来展示性能,设计人员必须自行构建器件库,并从SPICE开始进行建模。硅光子学的蓬勃发展,以及台积电进军硅光子学领域,有望在未来五年内带来更多结构和基础知识产权。像Synopsys和Cadence这样的公司确实提供硅光子学设计工具,但设计人员正在开发的许多结构都是全新的,需要从基础物理原理出发进行非常详细、耗时的底层建模。

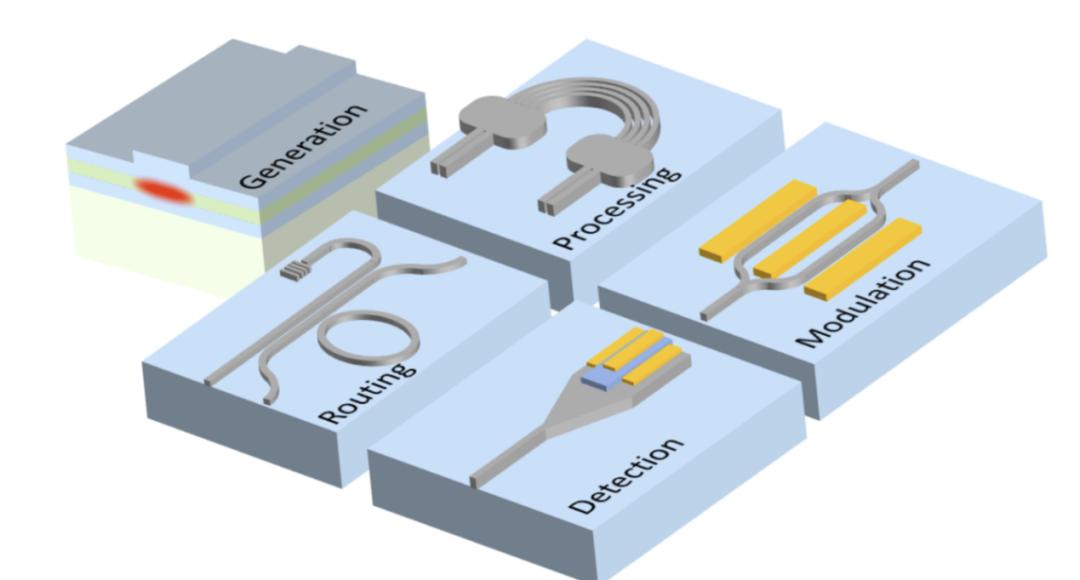

图 9:光子集成电路平台的典型库组件:生成、路由、处理、检测和调制

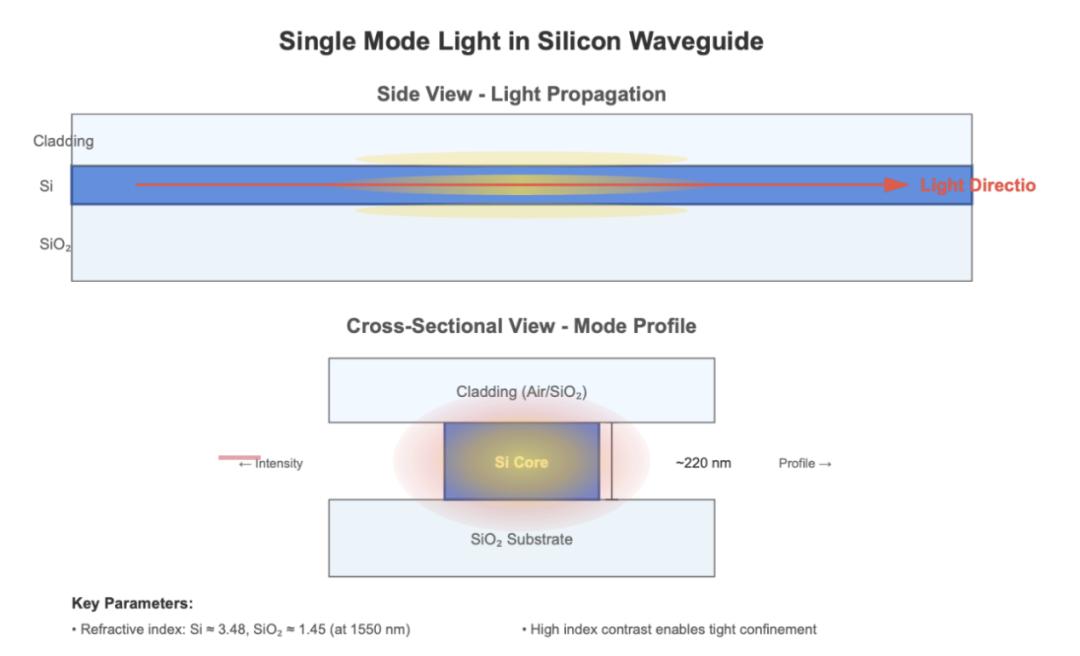

硅光子器件采用 200 毫米和 300 毫米晶圆制造,工艺精度可达 65 纳米。所用晶圆为 SOI 结构,并带有至少 1 微米厚的埋氧层(BOX:SiO2),用于光隔离。如下图所示,这是因为在硅(或氮化硅)波导中传输的单模光主要在硅波导芯内传播,但部分光场会“泄漏”到上方、侧面和下方的相邻材料中。因此,这些层必须足够厚,以防止光传播到其他有源区域。

图 10:波导中的单模光“泄漏”到周围材料中

硅光子学的一大挑战是信号损耗——波导输入端的信号强度会随着波导中每单位距离的传输而损耗。所有光器件都会产生信号损耗。如果信号损耗累积过高,信号强度将不足以正常工作。因此,在硅光子学设计中,对信号损耗的精确控制至关重要。

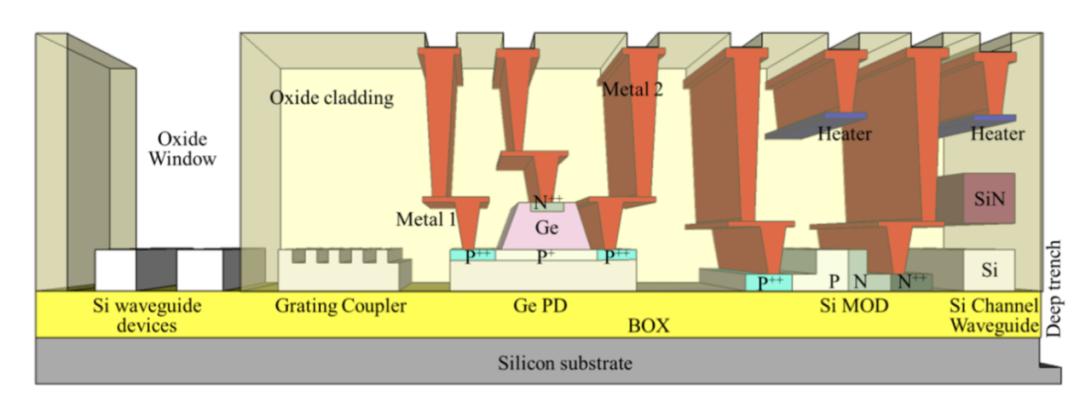

在硅光子学中,通常不使用CMOS晶体管(硅光子学和CMOS的集成已经开始——GF公司有一种将两者结合起来的工艺——但目前还不普遍)。硅光子学工艺中通常可用的器件包括:

1、布线:波导,由硅和氮化硅制成。波导需要一定的高度和宽度才能保证光的单模传输,并且波导周围需要有足够的材料,以防止光与其他元件发生相互作用。波导不能以90度角急转弯。弯曲需要一定的最小半径,以确保光在波导内发生折射。有趣的是,两个波导可以垂直交叉,且垂直光束之间的相互作用极小。这一点非常重要,因为许多代工厂只生产单层波导。

2、检测:检测分为两类:耦合器和光电探测器。耦合器用于捕获从光纤进入芯片的光。将光耦合到芯片的最有效方法是使用边缘耦合器,但光纤和芯片的对准可能具有挑战性。将光纤对准芯片以进行耦合的最简单方法是从上方使用光栅耦合器。一维光栅耦合器用于偏振光,二维光栅耦合器用于非偏振光。偏振光纤比标准单模光纤 (SMF) 贵得多,因此通常仅用于激光器到芯片的连接——激光器通过信号损耗较低的一维光栅耦合器连接到芯片。二维光栅耦合器可以捕获非偏振光,但体积更大、结构更复杂,并且信号损耗更大。它们用于数据信号。光电探测器用于将波导中的光强度转换为可由配套 CMOS 芯片读取的电信号。光电探测器采用锗制造,而锗并不是CMOS制造厂的常用材料。

3、调制:调制器用于将电信号转换到光信号上。在可插拔光器件中,调制器是马赫-曾德尔调制器。在CPO(耦合光子器件)中,调制器是微环,它是一种尺寸小得多的器件,对于缩小CPO芯片的尺寸至关重要,因为CPO芯片需要将数十根光纤集成到狭小的空间内,以便与GPU耦合。如下图所示,加热器用于控制调制器,根据来自配套CMOS芯片的电信号,将比特插入到输入的激光束中。在高速传输时,这需要高速PHY来驱动调制器。机械应力和电压也可以用作光子器件的控制手段。

4、处理方法:采用干涉仪配置的马赫-曾德尔器件可用于构建光开关,该开关接收两束入射光并分别输出两束光。通过控制加热器,该开关可以配置为输入0输出0、输入1输出1,或者输入0输出1、输入1输出0。这些开关的切换速度可达微秒级。

图 11:AMF(现为 GF)标准 MPW(多项目晶圆)流程的横截面视图

上图所示的氧化物窗口用于生物/化学光子传感器,使其能够与光场相互作用。这并非数据中心的应用。

通常,硅光子芯片不包含CMOS器件。与CMOS晶体管相比,光子器件的物理尺寸较大。例如,CMOS和SiPho芯片采用45nm工艺。尽管某些光子器件特性可以受益于先进的光刻技术,但光子技术短期内(甚至可能永远)都无法集成到3nm或2nm工艺中。

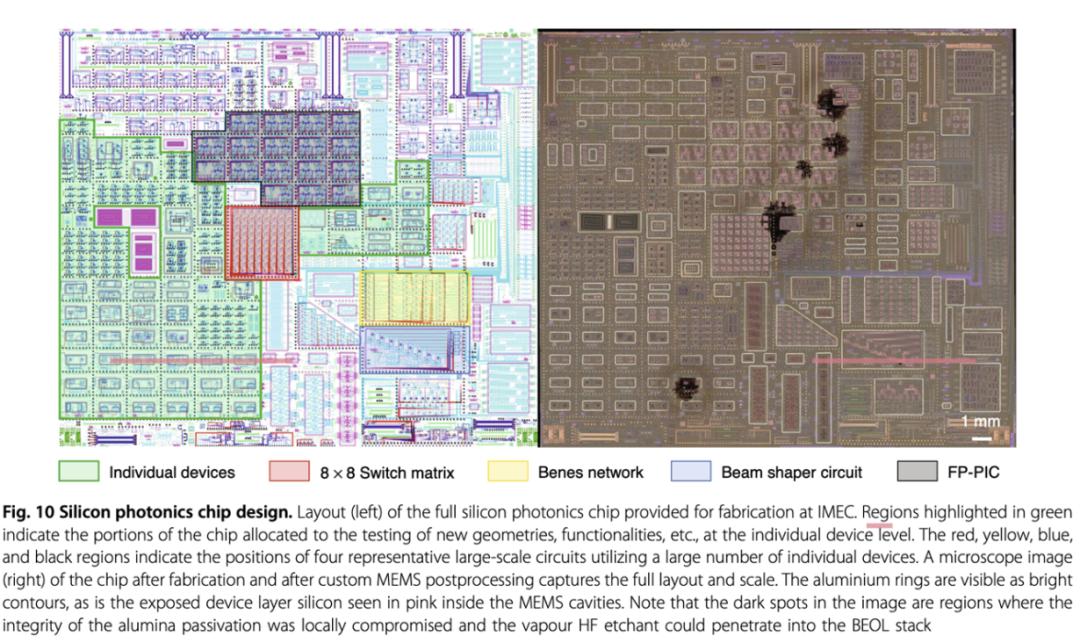

图 12:硅光子芯片的示意图和芯片照片

总结

利用硅光子技术,现在可以制造出能够对光进行复杂操控的芯片。如上图所示,这些结构体积庞大,类似于早期的CMOS工艺。硅光子技术在数据中心的主要功能是在高性能CMOS计算芯片和交换机之间,以及可能还有内存池之间进行数据传输。这些硅光子芯片将越来越多地集成到数据中心的每个单元中,我们将很快习惯于看到带有明亮黄色光纤的电路板,这些光纤传输着高带宽数据。服务器微处理器很可能也会采用这种技术,用光学器件取代PCIe(外围组件互连) 。

硅光子制造的产业结构也将发生类似的变革,晶圆收入将实现数量级增长,台积电有望凭借其在人工智能加速器(包括光引擎在内的所有芯片组件)制造中的作用,成为最大的供应商。台积电可能会像在CMOS领域一样,将许多架构和基础设施引入硅光子领域,从而以更短的时间和更低的成本开发出更复杂的光子芯片。