业界考虑进一步放宽未来 HBM 内存高度限制,混合键合导入恐再延后

20 小时前

/ 阅读约2分钟

来源:IT之家

HBM4世代主流堆叠层数为12/16层,JEDEC已放宽堆栈高度限制至775μm。面对20层堆叠需求,行业正考虑进一步放宽至800μm或更多,以避免大幅减薄DRAM晶圆导致的良率问题。

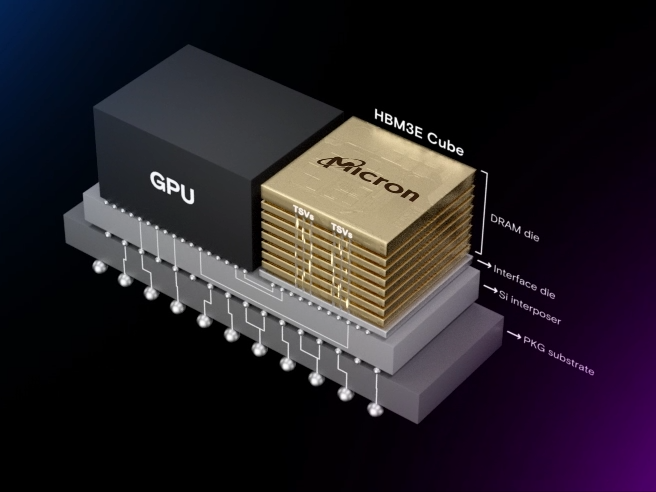

IT之家 3 月 8 日消息,HBM 高带宽内存的一大演进趋势是堆叠层数的增加,在目前的 HBM4 世代主流堆叠层数是 12 / 16。JEDEC 在制定 HBM4 规范时已经放宽了一次堆栈高度限制,从 720µm 提升到了 775μm。

而参考韩媒 ZDNET Korea 与 ETNEWS 的报道,面对下一代堆叠可达 20 层的 HBM,行业正在考虑进一步放宽高度限制至 800µm 乃至更多。

如果想在现有的 775μm 内以现有堆叠容纳 20 层 DRAM,则需要对 DRAM 晶圆进行大幅减薄,这会增加晶圆损坏的风险,进一步降低本已足够复杂的 HBM 的良率。

削减整体堆栈厚度的另一个方向是降低两层 DRAM 的间距,而这需要从键合方面着手。已被用于 NAND 闪存的混合(铜)键合可大幅度降低间距,但其技术难度极高的同时也需要大量的设备投资。如果高度限制被放宽,混合键合的导入也将被延后。

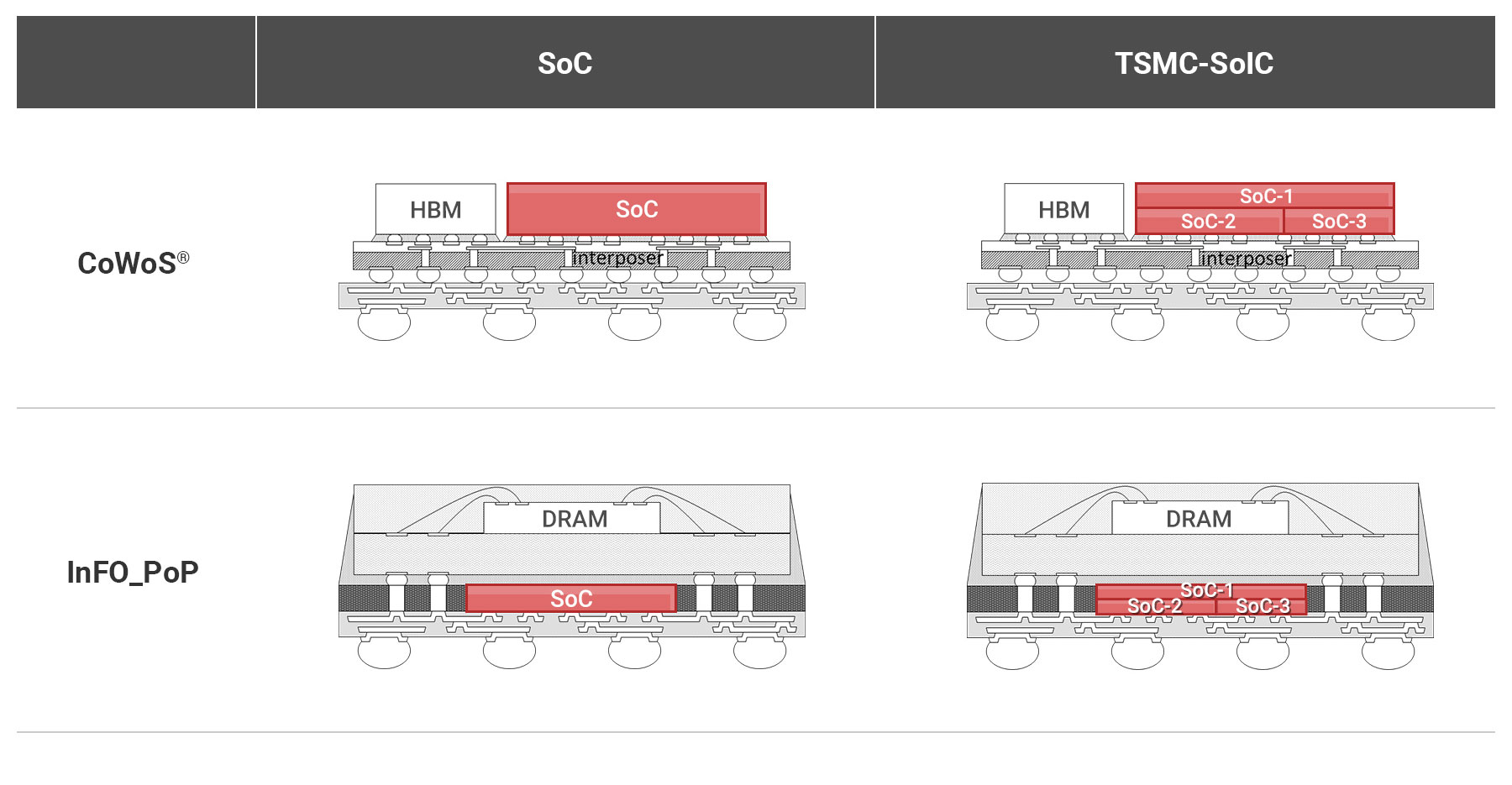

ZDNET Korea 还提供了另一个视角:台积电在先进封装领域占据主导地位,对标准的制定也有很大话语权。而台积电推动的 3D 先进封装技术 SoIC 会导致与 HBM 堆栈配套的 XPU 复合体增高,这为 HBM“长高”提供了天然裕量。