1.中科院新型光频梳光源,让光信号传输又快又节能;

2.中国科学院实验室成果入选ICCAD 2025并获后端最佳论文提名;

3.北京大学发布面向学术研究的开源围栅模型与预研工艺设计套件;

4.科研聚焦 | 南科大詹陈长课题组在JSSC发表DC-DC开关电源芯片研究成果;

1.中科院新型光频梳光源,让光信号传输又快又节能;

光频梳是高速光通信的基石。通过它实现并行数据传输,为破解传统光通信技术面临的带宽瓶颈和功耗难题提供了可能方案。然而,将光频梳推向大规模实用化仍是业界面临的一大挑战。

中国科学院半导体研究所陈思铭团队与其合作者,成功研制出一款可在140°C的极端温度下稳定工作的100GHz量子点光频梳激光器,为未来Tbps量级的光互连提供了至关重要的光源解决方案。

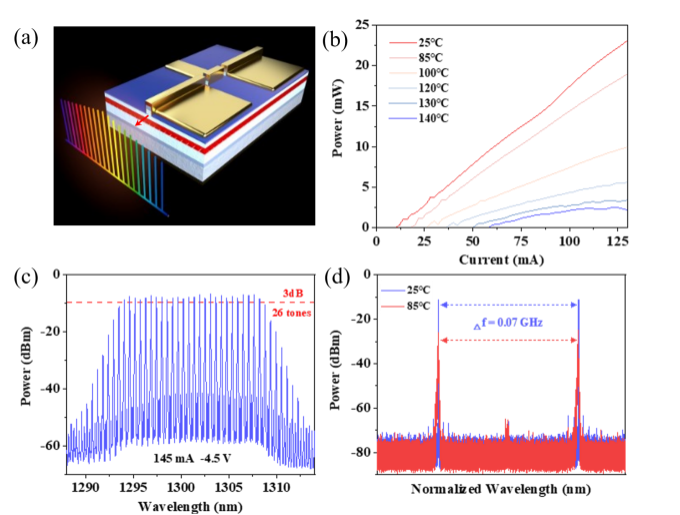

▲量子点锁模光频梳示意图及性能展示

能耗挑战下的光源需求

当前数据中心内部仍普遍依靠铜线传输电信号,电子在高速传输中产生巨大阻力与热量,随着人工智能的发展,其算力需求正以指数级攀升,其背后是惊人的能源消耗。

为构建新一代更快、更节能的光互连技术,业界正全力研发一种名为“共封装光学”(CPO)的革新性架构。有望将系统功耗降低30%至50%,并极大提升带宽密度。

然而,CPO技术成功的关键,在于紧邻着计算芯片的光学引擎——它必须具备极致的耐高温性、高效率、紧凑性与高可靠性,这是传统光源无法企及的严苛标准。

光频梳就像一把精密的“光梳子”,能同时产生数十乃至上百个稳定的光信道,相当于将单车道公路拓展为多个“车道”并跑,每条信道不仅频率精准,相位也高度同步,从而在大幅提升传输效率和稳定性的同时,显著缩小设备体积。

优质的光频梳还能覆盖很宽的频率范围,满足不同数据的传输需求。但要让这把“光梳子”在芯片旁的“火炉”中稳定工作,并兼具超宽带宽与超长寿命,实现难度极大。

CPO理想光源的突破

面对挑战,团队从材料、工艺到结构进行了系统性创新,研制出一种基于量子点材料的光频梳激光器。

在材料层面,激光器采用量子点这一纳米级半导体晶体作为增益介质。由于电子在其中受到三维空间的量子限制,其能级结构如同分立的原子,从而赋予了激光器卓越的温度稳定性与抗光反馈能力。

在工艺层面,针对传统n型或p型单种掺杂技术中低功耗与高耐热性难以兼顾的矛盾,团队创新性地采用“共掺杂”策略,巧妙地实现了二者的平衡与统一。

在结构层面,团队采用了“碰撞脉冲锁模”设计,通过光脉冲在腔内精确对撞直接倍增频率,在保证高输出功率的同时,满足了高速传输所需的100GHz宽信道间隔。

团队研制的光频梳激光器在工作温度、传输容量和可靠性方面均取得突破,展现出优越的综合性能:

在室温(25°C)下,激光器实现了14.312nm的3dB光学带宽,可产生26个并行信道,每个信道均可承载128Gb/s的PAM-4调制信号;在高达140°C的温度下,该器件仍保持稳定锁模;在85°C的工业级标准高温下,关键性能几乎无衰减,仍能支持22个信道稳定工作,实现总量2.816Tb/s的数据传输。

同时,该器件传输每比特数据的能耗在25°C和85°C下分别低至0.394pJ和0.532pJ。通过在85°C高温下进行超过1500小时的加速老化实验推算,其平均无故障时间长达207年,完全满足严苛的商业应用要求。

该器件利用量子点材料对光反馈不敏感的特性,省去了传统系统中昂贵且笨重的光隔离器,从而大幅减轻了系统在尺寸、重量和成本上的压力。

赋能未来

该项工作不仅在实验上验证了在单一芯片上同时实现超高宽带、耐高温、长寿命和高集成度量子点光频梳的可行性,更为下一代数据中心与AI算力集群的光互连系统,提供了一条性能强大且兼具高经济效益的光源实现路径。

未来,随着这项技术的成熟和应用,我们的数据传输将变得更快、更稳定、更节能,为人工智能、云计算等前沿领域的发展注入源源不断的强劲动力。

2.中国科学院实验室成果入选ICCAD 2025并获后端最佳论文提名;

国际计算机辅助设计大会(International Conference on Computer-Aided Design,ICCAD),是电子设计自动化(EDA)和计算机辅助设计领域的顶级会议之一,2025年该会议在德国慕尼黑举办。实验室论文《CLASS: A Controller-Centric Layout Synthesizer for Dynamic Quantum Circuits》被ICCAD 2025接收,并获得后端最佳论文提名。该论文共同第一作者为实验室智能计算机课题组博士生陈禹和赵逸伦,指导教师为王颖研究员和韩银和研究员。

从“量子芯片”到“控制器”:重新定义布局综合问题

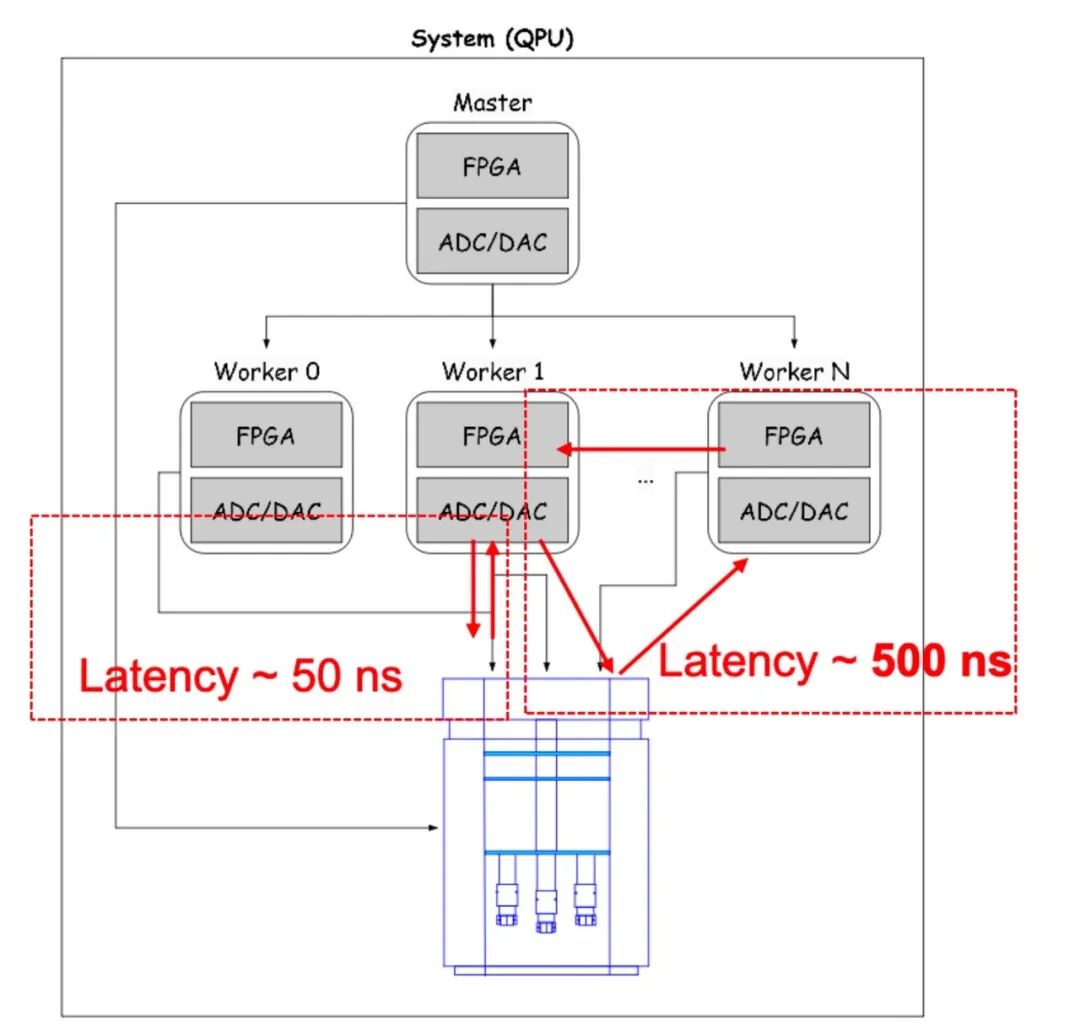

在经典计算机中,EDA工具通过自动化设计实现从逻辑综合到布局布线的全流程优化。而在量子计算机中,“布局综合(Layout Synthesis)”承担着类似角色,是量子算法映射到物理硬件的关键步骤。然而,随着量子比特数从几十迈向上千甚至上百万规模,量子系统的控制架构也从单控制器演化为多控制器协同架构。这类分布式控制架构由多个量子控制处理器(Quantum Control Processor, QCP)互联组成——它们共同驱动量子芯片执行复杂的量子操作。

在这种架构下,控制器间通信延迟成为系统性能的最大瓶颈。尤其是在执行动态量子电路(Dynamic Quantum Circuits)时,这一问题尤为突出。动态电路允许在计算过程中根据测量结果“前馈”调整后续操作,这是量子纠错、量子隐形传态等核心算法的基础。但如果测量结果需要跨控制器传输,就会引入严重延迟,造成量子态退相干(Decoherence)——即计算失效。

CLASS:以控制器为中心的量子布局综合新模式

为应对这一挑战,研究团队提出了CLASS(Controller-centric Layout Synthesizer System)——首个面向动态量子电路的控制器感知布局综合框架。与传统“以量子芯片为中心”的方法不同,CLASS将优化重心转向“以控制器为中心”,并创新性地将布局问题建模为超图最小割(Hypergraph Min-Cut)问题。

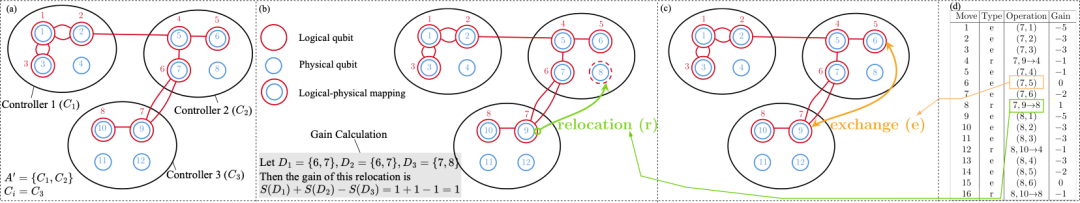

其核心算法分为两阶段:

1. 初始布局生成:基于贪心策略,将强依赖的量子比特优先分配至同一控制器。

2. 迭代优化阶段:通过量子比特迁移与门级调度协同优化,进一步减少跨控制器通信。

对于存在拓扑约束的量子芯片,CLASS还引入了延迟感知门调度器(Latency-Aware Scheduler),在插入SWAP门时同时权衡电路深度与通信时延。

在多项标准测试电路中,CLASS实现了平均48.45%的跨控制器通信减少,部分电路的通信成本降至零,同时量子操作数仅增加约2.10%。这意味着CLASS在保持电路正确性的同时显著提升执行效率,适用于当前超导、离子阱等主流技术路线在扩展到百比特以上规模时面临的控制瓶颈问题,为未来大规模量子计算的可扩展性提供技术基础。

该研究兼具应用价值,CLASS可作为量子EDA中的节点工具,直接集成至国产量子计算云平台(如OriginQ、Quafu等)的编译器工具链中,为量子系统在芯片-控制协同设计和软硬件适配方面提供新思路。

图1 QPU(量子处理器)控制架构中的测量-前馈路径及其时延

图2 CLASS基于量子比特移动的迭代优化减少跨控制器通信

处理器芯片全国重点实验室依托中国科学院计算技术研究所,是中国科学院批准正式启动建设的首批重点实验室之一,并被科技部遴选为首批 20个标杆全国重点实验室,2022年5月开始建设。实验室学术委员会主任为孙凝晖院士,实验室主任为陈云霁研究员。实验室近年来获得了处理器芯片领域首个国家自然科学奖等6项国家级科技奖励;在处理器芯片领域国际顶级会议发表论文的数量长期列居中国第一;在国际上成功开创了深度学习处理器等热门研究方向;直接或间接孵化了总市值数千亿元的国产处理器产业头部企业。

3.北京大学发布面向学术研究的开源围栅模型与预研工艺设计套件;

近日,北京大学微纳电子器件与集成技术全国重点实验室发布了面向围栅(GAA)纳米片技术、具有自主知识产权的系列模型PHIMO,以及基于PHIMO的预研类工艺设计套件PKP,为集成电路领域的教学与学术研究提供了基础支撑。

器件集约模型(Compact Model)与工艺设计套件(Process Design Kit, 简称PDK)是连通集成电路设计和制造的桥梁。电子设计自动化(EDA)工具与PDK紧密配合,支持基于该工艺的电路设计。为了支撑面向先进工艺的教学与科研,需要具有预研属性的虚拟PDK(Virtual PDK),例如亚利桑那大学开源的ASAP7。预研类PDK不与任何实质的工艺制程关联,通过整合关键的趋势性预测,为相关方向的前沿学术研究提供基础支撑。

基于此目的,北京大学建立了自主知识产权的器件模型与预研PDK系列:PKP(Peking University Predictive PDK)。此次发布的是面向3纳米围栅纳米片技术的开源预研套件PKP3,包含了北京大学提出并发展的PHIMO系列集约模型、基于虚拟设计规则的PCell、标准单元库和SRAM单元的设计,不同阈值电压的器件也假设了多个工艺角。

微纳电子器件与集成技术全国重点实验室此次开源发布PKP3,期望与从事集成电路学术研究的院校及研究机构携手,共同建设集成电路前沿技术的生态,推动学术研究、课程教学、人才培养的新发展。后续还将基于我国的汉擎PDK标准持续推动PKP系列的建设。

4.科研聚焦 | 南科大詹陈长课题组在JSSC发表DC-DC开关电源芯片研究成果;

近日,南方科技大学深港微电子学院詹陈长副教授课题组在DC-DC开关电源芯片领域取得重要突破。课题组博士研究生张年提出了一种具备高轻载效率与隐性隔离侧反馈机制的Fly-buck (飞降压) 型DC-DC转换器。相关成果以 “A Light-Load Optimized 7–100-V Dual-Output Fly-Buck Converter With an Implicit Feedback of the Isolated Output in DCM” [1]为题发表在集成电路设计领域顶级期刊《固态电路杂志》(IEEE Journal of Solid-State Circuits, JSSC)上。

Fly-buck转换器能够以较低成本实现一个非隔离输出与多个隔离输出,广泛应用于工业电源、两轮电动车BMS保护板等场景。然而,传统架构为保证隔离侧负载能力,需工作在强制连续导通模式(FCCM)下,即使在轻载条件下仍需保持高开关频率,导致开关损耗大、效率降低。为此,研究团队在论文[1]中提出了一种创新的限制零电流时间的断续导通模式,并结合具有隔离侧输出隐性反馈机制的增强型导通时间发生器,在轻载时显著降低开关频率,提升能效,同时保障了隔离侧负载能力。

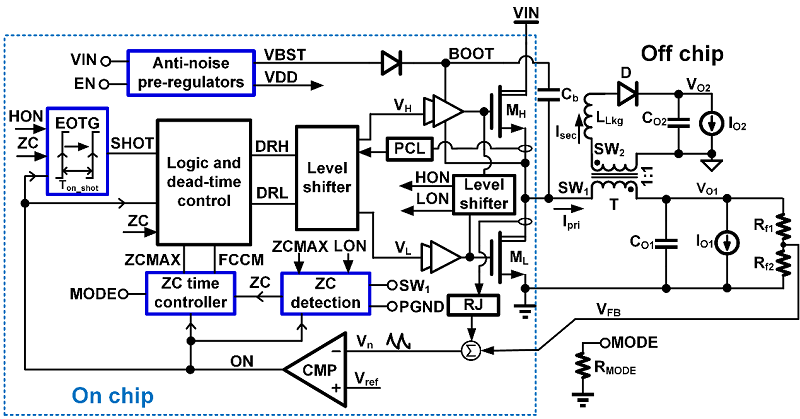

图1 具有隔离侧隐性反馈的Fly-buck转换器的结构图

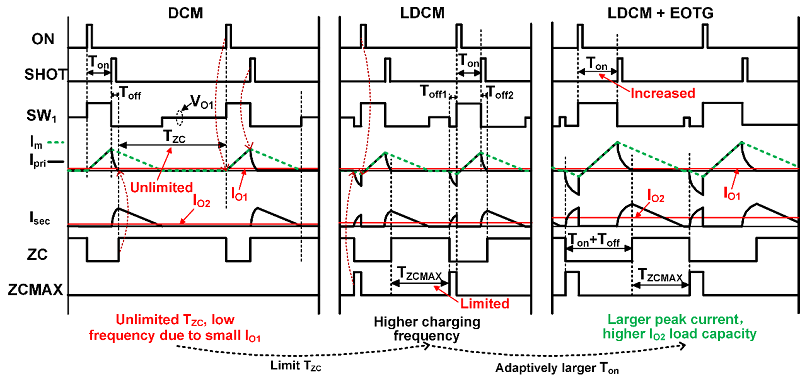

图2 不同工作模式的时序图

图1展示了论文[1]中提出的具有隔离侧隐性反馈的Fly-buck转换器的结构图,图2则为Fly-buck转换器在不同工作模式下的时序图。其核心改进在于,通过零电流时间控制器限制零电流时间,相较于传统DCM模式,这一措施提升了隔离侧的负载能力;而与FCCM模式相比,则能通过降低开关频率来提高效率。在此基础上,系统采用增强型导通时间发生器(EOTG)实现隔离侧的隐性反馈,在隔离侧输出下降时自适应增大导通时间,进一步增强了隔离侧的带载能力,确保系统在实际应用中的负载需求得到满足。

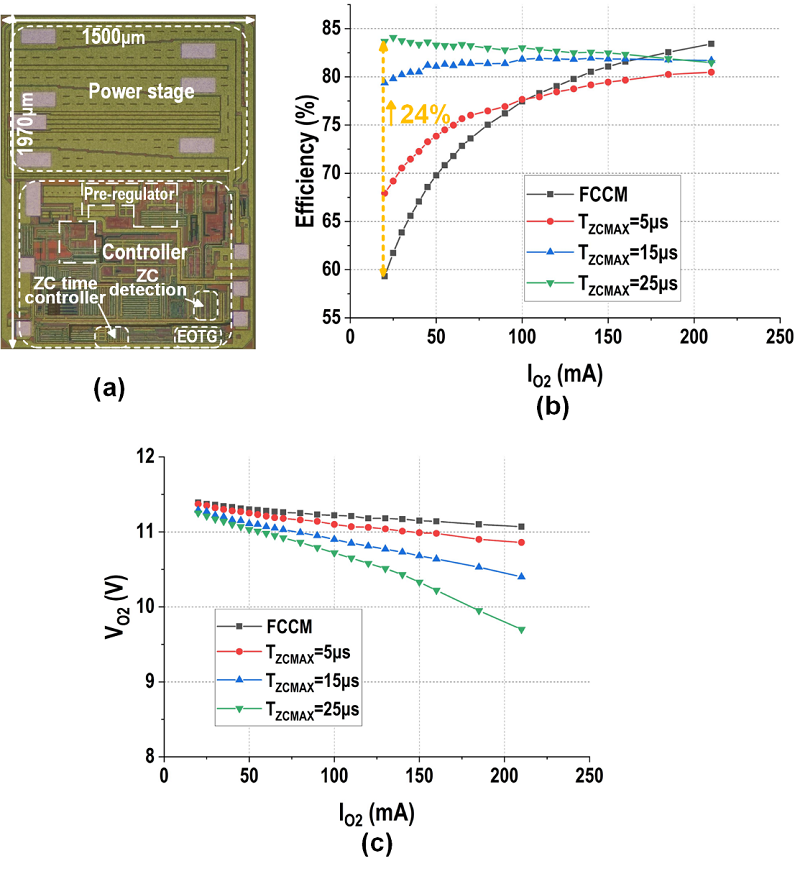

图 3 (a) 芯片照片;(b) 测试得到的不同零电流时间限制下的转换效率;(c) 测试得到的不同零电流时间限制下的隔离侧输出电压

图3展示了芯片显微照片及关键性能测试结果。在48 V输入条件下,实测显示其轻载效率相比FCCM模式最高可提升24%,且在隔离侧负载电流不超过150mA时,输出电压跌落控制在10%以内,处于可接受范围。与DCM模式相比,该设计的隔离侧带载能力已实现了大幅提升。

本研究由南方科技大学深港微电子学院詹陈长副教授团队与茂睿芯(深圳)科技有限公司合作完成。南方科技大学深港微电子学院为论文的第一单位及通讯单位。课题组博士研究生张年为论文的第一作者,詹陈长副教授为论文通讯作者。本研究得到了国家自然科学基金委员会、深圳市科技创新委员会以及相关企业横向课题的经费资助,并得到了茂睿芯-深港微电子学院先进绿色能源管理芯片联合实验室的支持。