过去两年是高数值孔径极紫外光刻技术发展的重要篇章。随着首批系统交付客户,以及ASML与imec联合成立的高数值孔径极紫外光刻实验室的启动——这为整个生态系统提供了早期探索其潜力的机会——这项技术正获得真正的发展动力。目前,高数值孔径极紫外光刻技术展现出巨大的潜力,有望实现其在尺寸微缩、工艺简化和设计灵活性方面的承诺。

释放这些能力源于一种整体方法,该方法同时优化材料和图案化工艺、掩模和成像技术、光刻增强技术(例如光学邻近校正 (OPC))、计量和检测以及设计 。这是imec-ASML高数值孔径EUV生态系统内强大合作的成果,该生态系统涵盖了领先的芯片制造商、设备、材料和光刻胶供应商、掩模公司以及计量专家。

本文探讨了高数值孔径 EUV 光刻技术背后的关键驱动因素,并重点介绍了光刻和图案化生态系统发展中的转折点,这些转折点使得该技术得以进行实验验证。

更高的分辨率和图像对比度

与 0.33NA EUV 光刻相比,0.55NA EUV 光刻的数值孔径 (NA) 提高了 67%,因此有望获得更高的分辨率。

解析间距小至 16 纳米的线条:世界纪录

光刻系统的分辨率反映了该工具打印和分辨特定间距或关键尺寸 (CD) 特征的能力。瑞利方程提供了三个提高分辨率的途径:使用更小的 k1 因子、使用更短波长的光以及提高系统投影镜头的数值孔径 (NA)。k1 因子取决于许多与芯片制造工艺相关的因素,为了提高分辨率,通常会尽可能接近其物理极限 0.25。NA 控制用于成像的光量(更准确地说,是镜头捕获的衍射级数)。低 NA (0.33) 和高 NA (0.55) EUV 光刻均使用波长为 13.5nm 的光。但高 NA EUV 的 NA 值比低 NA EUV 高 67%,这使其在分辨率方面具有明显优势,最终有望分辨出间距小至 16nm(或 CD 为 8nm)的线条。

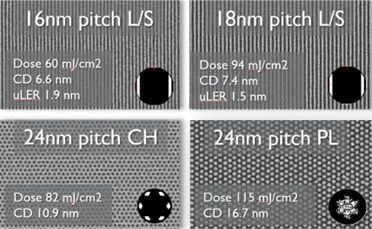

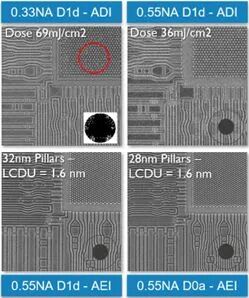

2024年,imec在ASML-imec高数值孔径EUV光刻实验室中,利用0.55NA EUV光刻扫描仪(TWINSCAN EXE:5000)实现了16nm间距线/空的单次打印图像,创造了世界纪录。这些图像打印在专为高数值孔径EUV光刻优化的金属氧化物光刻胶(MOR)上。同样,接触孔(打印在化学放大光刻胶(CAR)上)和柱状结构(打印在MOR上)也展现了令人瞩目的24nm间距(中心距)分辨率。

然而,最终分辨率仅仅是一个“光学”上的承诺,它反映的是图像在照射到晶圆之前空中成像的质量。在晶圆曝光过程中,空中成像会在光刻胶中形成图案,这些图案在显影后会被进一步蚀刻到下层材料中。因此,最终图案化结构的分辨率也取决于图案化过程中使用的材料(光刻胶、下层材料、硬掩模等)和蚀刻工艺的性能。工艺限制也可能影响300mm晶圆上最终结构的良率。

因此,高数值孔径极紫外光刻技术(High NA EUV)实现工业相关图案化结构的分辨率极限将大于16nm间距。先进的光刻材料研发工作,特别是新型材料和磁光刻(MOR)技术的研发,对于使图案化技术的分辨率尽可能接近高数值孔径极紫外光刻技术的理论极限至关重要。

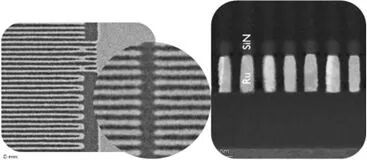

2025年,imec展示了20nm间距的金属化线结构,该结构适用于工业级镶嵌金属化工艺;此外,还展示了采用直接金属刻蚀(DME)金属化方案获得的20nm和18nm间距的钌线。这种极高的分辨率是通过一种整体方法实现的,该方法涉及对光学邻近校正(OPC)技术、光掩模、光刻胶、底层、刻蚀工艺和材料的协同优化。

工艺简化

芯片行业可能会辩称,20nm 的特征尺寸也可以使用低数值孔径 (Low NA) 的极紫外 (EUV) 光刻技术进行图案化。诚然如此,但这只能通过复杂的多次曝光步骤来实现。这涉及到将芯片图案分割成两个或多个“更简单”的掩模,从而增加制造时间、降低良率、增加碳排放并提高成本。而高数值孔径 (High NA) 的极紫外光刻技术所提供的高分辨率则减少了多次曝光的需求,使得最小的芯片特征尺寸能够在一次曝光中完成印刷。

逻辑路线图:逻辑 A14 和 A10 关键金属层的单次图案化

对于 A14 和 A10 逻辑节点,最关键的金属层(即 M0 和 M2)的要求非常苛刻:线/间距 ≤20nm,用于中断线的密集端对端 (T2T) 结构(行业目标是 T2T 的 CD ≤15nm,LCDU ≤3nm),以及中心距 ≤30nm 的随机通孔。0.33NA EUV 光刻需要 3-4 个掩模才能完成这些特征的图案化,而 0.55NA EUV 光刻只需一次曝光即可完成,实验已证实这一点。Imec 还可以克服实现良好 T2T 控制的挑战:通过协同优化光源、掩模(使用低 n 相移掩模)、光刻胶和刻蚀工艺(使用定向刻蚀技术),可以实现 13nm T2T 结构低于 3nm 的目标 LCDU 。

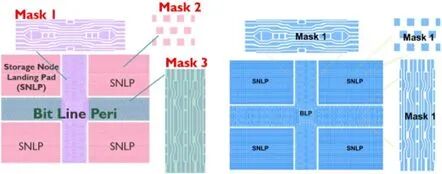

DRAM路线图:D1d和D0a位线周边/存储节点,着陆焊盘层的单次图案化

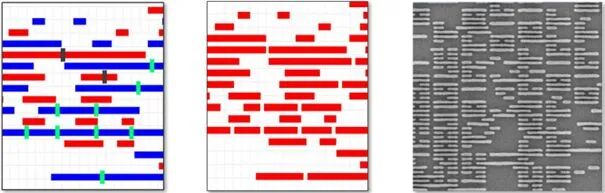

高数值孔径极紫外光刻技术能够省去复杂的多重曝光步骤,使其成为未来DRAM节点(例如32nm (D1d) 和28nm (D0a) DRAM)发展路线图的关键技术。对于这些节点,实验已证实使用高数值孔径极紫外光刻技术对BLP/SNLP层(包含位线外围和存储节点焊盘的层)进行图案化的可行性。0.33NA极紫外光刻技术至少需要三个掩模才能对这些BLP/SNLP层进行图案化,而0.55NA极紫外光刻技术仅需一个掩模即可完成相同的任务。

设计灵活性

在2000年代中后期,先进逻辑芯片的设计在最关键的层中从二维电路布局转向了一维曼哈顿布局。这种设计上的“代价”是为了扩展193nm浸没式光刻技术的应用范围,使其能够实现更低k1值的单次曝光和多次曝光,从而为0.33NA EUV光刻技术的成熟做好准备。在二维双向设计中,曼哈顿几何结构用于在垂直和水平方向上形成电路。相比之下,一维或单向设计则仅在每一层中沿垂直或水平方向排列结构。尽管一维曼哈顿布局能够提供高密度的表示,但它也存在一些局限性。例如,当需要将一条金属线与相邻的金属线连接时,必须增加一层带有通孔的结构——这不仅会增加晶圆成本,还会增加电流路径的长度。

高数值孔径极紫外光刻技术带来的分辨率飞跃,使1.5D和2D曼哈顿式设计得以重新应用,甚至能够引入曲线几何形状和路径。这不仅为芯片设计人员提供了更大的灵活性,从而提升功耗和性能,而且还有可能减少芯片面积或层数,进而降低成本。

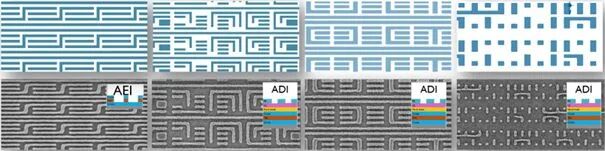

高数值孔径极紫外光刻技术可实现,二维设计的双向布线

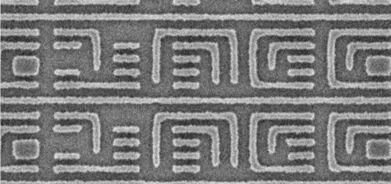

Imec 及其合作伙伴演示了使用 2D Manhattan 设计对 22nm 和 28nm 间距线结构进行双向布线。OPC 优化和掩模制作质量使得 2D 设计在蚀刻后能够实现设计意图与晶圆数据之间良好的图案保真度。

与曲线设计技术的兼容性

此外,imec 还开发了一种解决方案,用于在芯片设计阶段引入更复杂的曲线几何形状,从而将曲线设计的应用范围扩展到光刻和掩模阶段之外。曲线设计已被证明对多种应用场景都有益,从标准单元设计到源/漏极接触和栅极重新布线,再到布局布线设计。例如,在标准单元设计中,曲线设计可以在放宽 M0 间距的同时,实现 20% 的面积缩减。imec 最近展示了曲线设计形状与高数值孔径 EUV 光刻技术的兼容性,从而能够充分利用高数值孔径 EUV 光刻技术在先进节点上带来的分辨率提升。

结论

开发高数值孔径(High-NA)专用光刻和图案化技术需要采用整体方法,才能验证其三大优势:相较于0.33NA EUV光刻技术,在分辨率和图像对比度方面实现提升;通过单次图案化简化工艺;以及通过1.5D、2D和曲面设计实现设计灵活性。Imec及其合作伙伴生态系统正不断突破这些技术的极限,开发下一代高数值孔径EUV光刻技术,为业界提供均衡的选择。目前,研发工作正致力于解决诸如景深提升、随机缺陷抑制和拼接技术等挑战。

因此,高数值孔径极紫外光刻技术将成为未来先进技术(例如先进人工智能芯片、高性能计算和下一代存储器)的关键推动因素。它被视为满足人工智能和数据中心应用需求的必要条件,因为这些应用需要硬件快速发展。该技术在实现《欧洲芯片法案》中关于推动2纳米以下逻辑技术节点的目标方面也发挥着关键作用。